**Lehrstuhl für Informatik 10 (Systemsimulation)**

**Optimierung des Red-Black-Gauss-Seidel-Verfahrens

auf ausgewählten x86-Prozessoren**

Markus Stürmer

Studienarbeit

# **Optimierung des Red-Black-Gauss-Seidel-Verfahrens auf ausgewählten x86-Prozessoren**

**Markus Stürmer**

Studienarbeit

Aufgabensteller: Prof. Dr. U. Rüde

Betreuer: Dipl.-Inf. J. Treibig

Bearbeitungszeitraum: Dezember 2004 – August 2005

**Erklärung:**

Ich versichere, daß ich die Arbeit ohne fremde Hilfe und ohne Benutzung anderer als der angegebenen Quellen angefertigt habe und daß die Arbeit in gleicher oder ähnlicher Form noch keiner anderen Prüfungsbehörde vorgelegen hat und von dieser als Teil einer Prüfungsleistung angenommen wurde. Alle Ausführungen, die wörtlich oder sinngemäß übernommen wurden, sind als solche gekennzeichnet.

Erlangen, den 4. August 2005

.....

# Inhaltsverzeichnis

|                                                                                       |           |

|---------------------------------------------------------------------------------------|-----------|

| <b>1 Motivation</b>                                                                   | <b>1</b>  |

| <b>2 Modellproblem und Red-Black Gauss-Seidel</b>                                     | <b>2</b>  |

| 2.1 Gauss-Seidel-Verfahren . . . . .                                                  | 2         |

| 2.2 Diskretisierung der Poisson-Gleichung . . . . .                                   | 3         |

| 2.2.1 2D Fall . . . . .                                                               | 4         |

| 2.2.2 3D Fall . . . . .                                                               | 5         |

| 2.3 Anwendung auf das Modellproblem und Variante des Red-Black Gauss-Seidel . . . . . | 7         |

| 2.4 Implementierung . . . . .                                                         | 8         |

| <b>3 Wichtige Konzepte zur Steigerung der Prozessorleistung</b>                       | <b>12</b> |

| 3.1 Erhöhung des Instruktionsdurchsatzes . . . . .                                    | 12        |

| 3.1.1 Pipelining und Superpipelining . . . . .                                        | 12        |

| 3.1.2 Speculative Execution . . . . .                                                 | 13        |

| 3.1.3 Out of Order Execution . . . . .                                                | 13        |

| 3.1.4 Superscalarity . . . . .                                                        | 13        |

| 3.1.5 Chaining . . . . .                                                              | 13        |

| 3.1.6 SIMD . . . . .                                                                  | 14        |

| 3.2 Erhöhung des Speicherdurchsatzes . . . . .                                        | 14        |

| 3.2.1 Caches . . . . .                                                                | 14        |

| 3.2.2 Prefetching . . . . .                                                           | 14        |

| 3.2.3 Write Combining . . . . .                                                       | 15        |

| <b>4 Vorstellung der Test-Systeme</b>                                                 | <b>16</b> |

| 4.1 Intel Pentium 4 Prescott 3,2 GHz<br>fauia42.informatik.uni-erlangen.de . . . . .  | 16        |

| 4.1.1 Befehls- und Registersatz . . . . .                                             | 16        |

| 4.1.2 Prozessorkern . . . . .                                                         | 17        |

| 4.1.3 Speicherhierarchie . . . . .                                                    | 18        |

| 4.1.4 Prefetcher . . . . .                                                            | 18        |

| 4.2 AMD Athlon64 4000+ 2,4 GHz<br>fauia49.informatik.uni-erlangen.de . . . . .        | 18        |

| 4.2.1 Befehls- und Registersatz . . . . .                                             | 19        |

| 4.2.2 Prozessorkern . . . . .                                                         | 19        |

| 4.2.3 Speicherhierarchie . . . . .                                                    | 20        |

| 4.2.4 Prefetcher . . . . .                                                            | 20        |

| <b>5 Angewandte Optimierungsverfahren</b>                                             | <b>21</b> |

| 5.1 Datenlayout . . . . .                                                             | 21        |

| 5.1.1 Anpassung des Datenlayouts für 2D . . . . .                                     | 21        |

| 5.1.2 Erweiterung auf 3D . . . . .                                                    | 25        |

| 5.2 Code-Optimierung . . . . .                                                        | 27        |

| 5.2.1 Ablaufkontrolle und Adressierung . . . . .                                      | 27        |

| 5.2.2 Ausführung der Berechnungen . . . . .                                           | 27        |

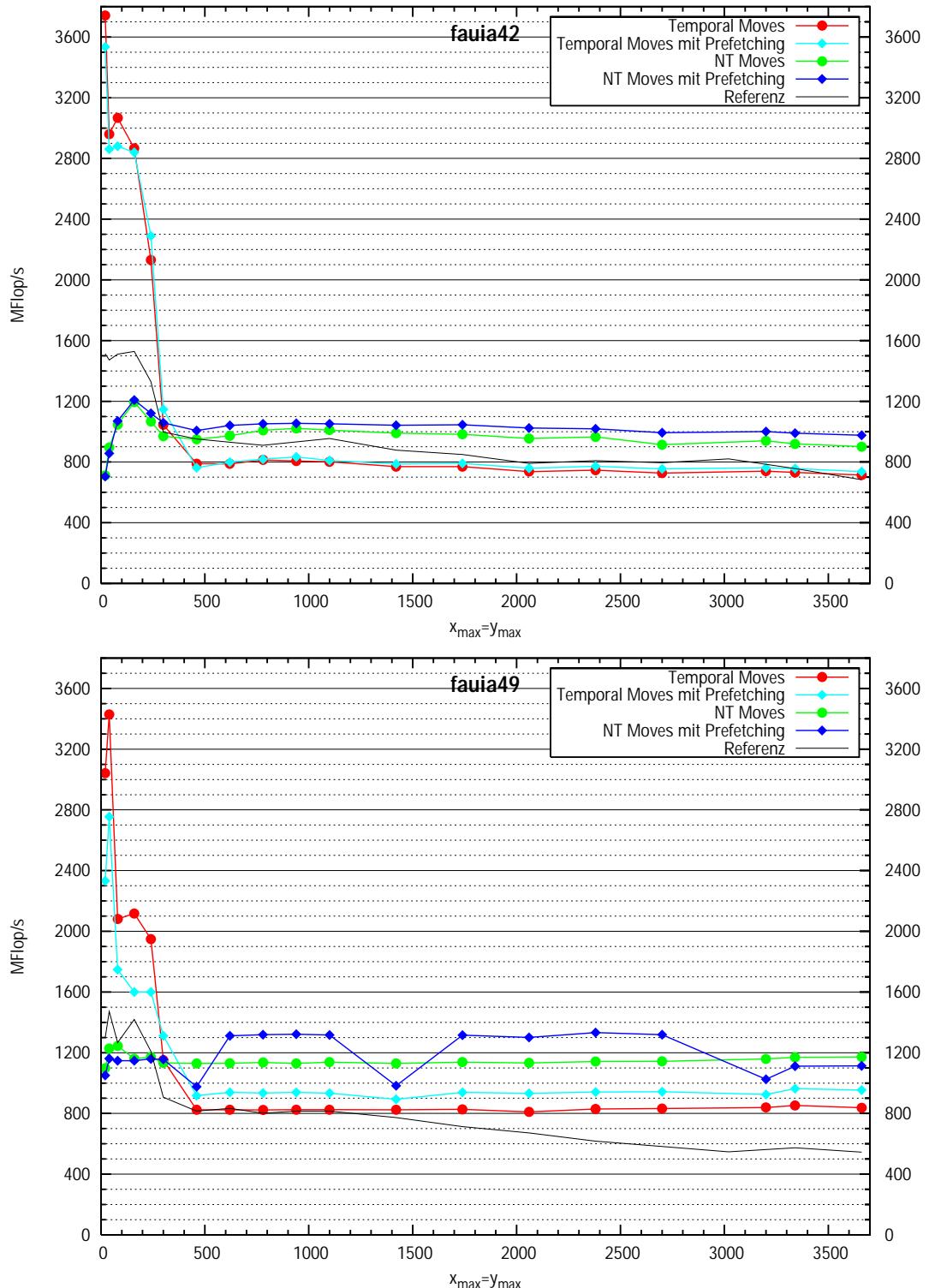

| 5.3 Non-Temporal Moves . . . . .                                                      | 28        |

|          |                                                                   |           |

|----------|-------------------------------------------------------------------|-----------|

| 5.4      | Blocking . . . . .                                                | 28        |

| 5.4.1    | Blocking für den 2D Red-Black Gauss-Seidel . . . . .              | 30        |

| 5.4.2    | Blocking für den 3D Red-Black Gauss-Seidel . . . . .              | 32        |

| 5.5      | Software Prefetching . . . . .                                    | 34        |

| <b>6</b> | <b>Benchmarking</b>                                               | <b>36</b> |

| 6.1      | Getestete Implementationen . . . . .                              | 36        |

| 6.1.1    | Red-Black Gauss-Seidel in 2D . . . . .                            | 36        |

| 6.1.2    | Red-Black Gauss-Seidel in 3D . . . . .                            | 37        |

| 6.2      | Referenz-Implementationen . . . . .                               | 38        |

| 6.2.1    | Referenz für den 2D Red-Black Gauss-Seidel . . . . .              | 38        |

| 6.2.2    | Referenz für den 3D Red-Black Gauss-Seidel . . . . .              | 43        |

| 6.3      | Theoretische Vergleichswerte . . . . .                            | 45        |

| 6.3.1    | Instruktionsdurchsatz . . . . .                                   | 45        |

| 6.3.2    | Minimaler Hauptspeicherdurchsatz . . . . .                        | 46        |

| 6.3.3    | Prozessor I/O . . . . .                                           | 47        |

| <b>7</b> | <b>Bewertung der Optimierungen</b>                                | <b>48</b> |

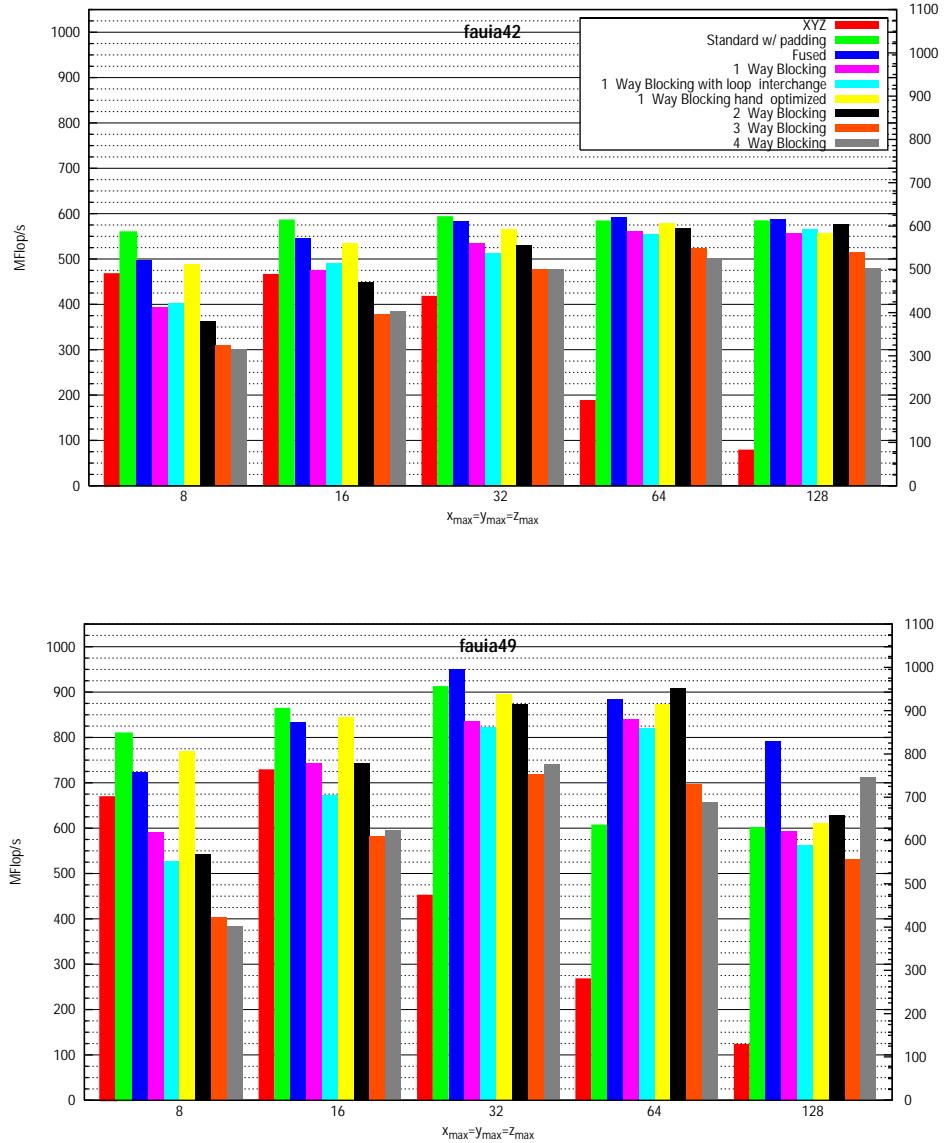

| 7.1      | Vektorisierung und Speicherlayout . . . . .                       | 48        |

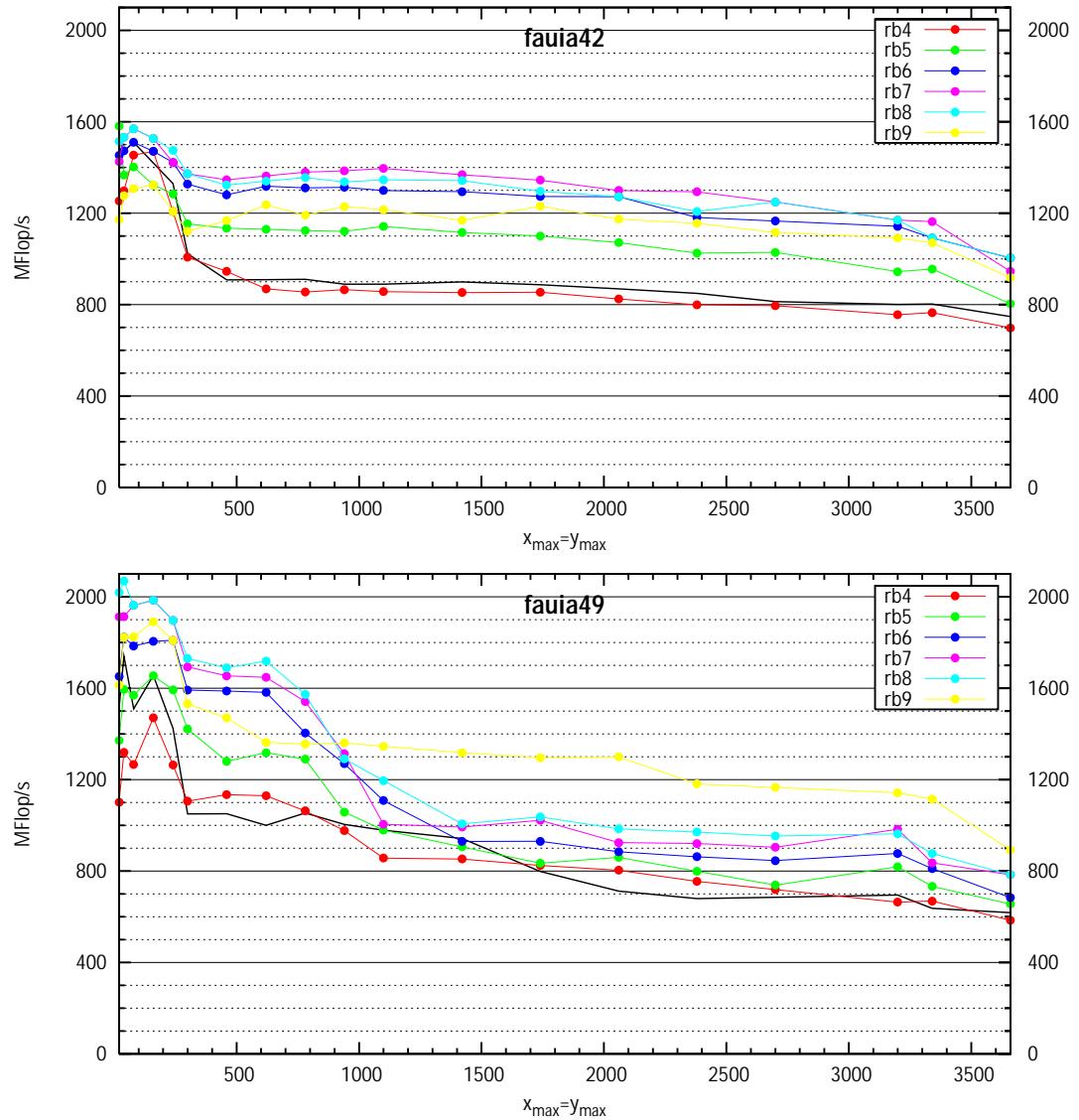

| 7.1.1    | 2D Red-Black Gauss-Seidel mit einzelnen Halbiterationen . . . . . | 48        |

| 7.1.2    | 3D Red-Black Gauss-Seidel mit einzelnen Halbiterationen . . . . . | 50        |

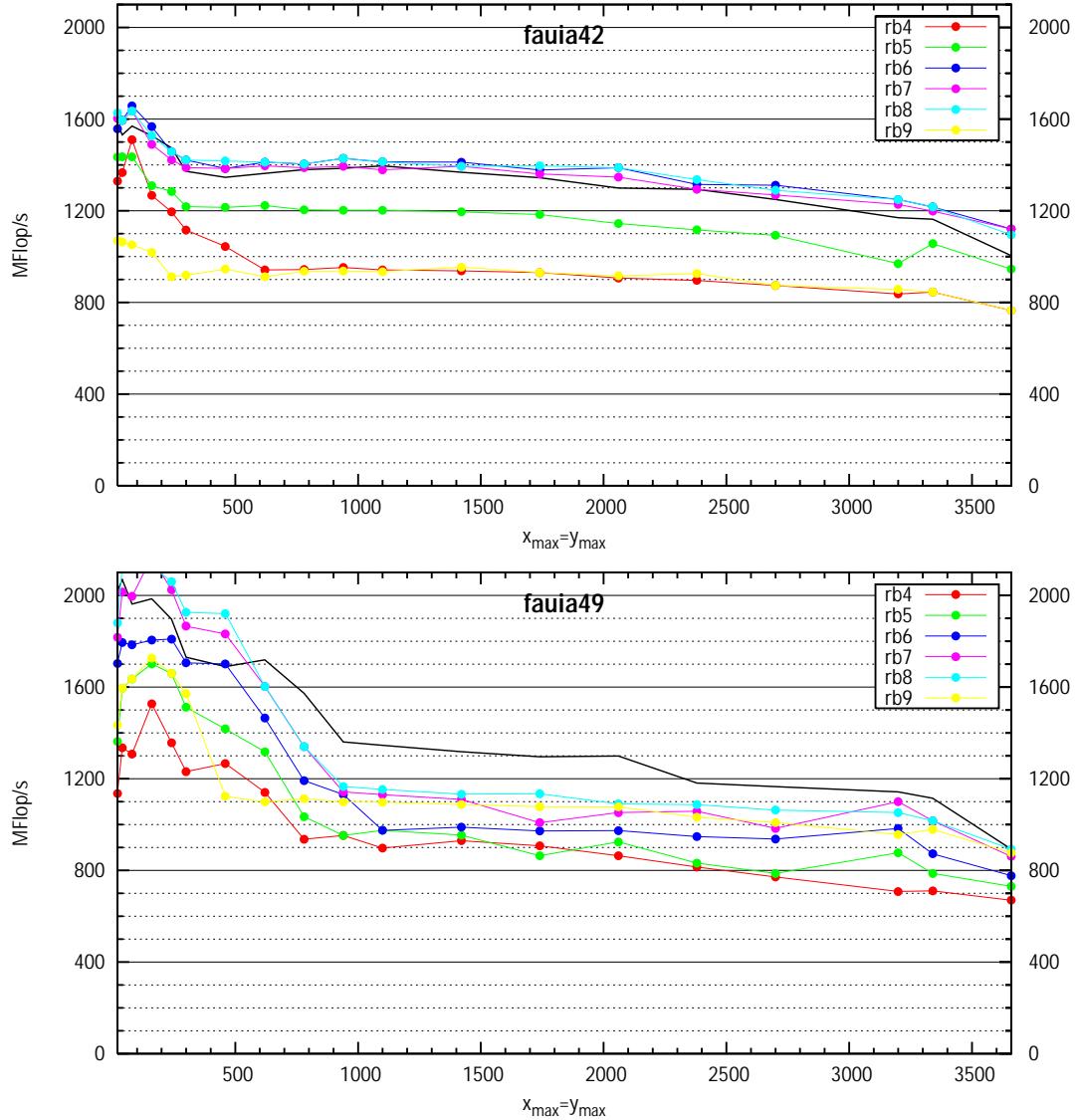

| 7.2      | Blocking-Verfahren . . . . .                                      | 52        |

| 7.2.1    | Blocking in 2D . . . . .                                          | 52        |

| 7.2.2    | Blocking in 3D . . . . .                                          | 56        |

| 7.3      | Tabellen . . . . .                                                | 60        |

# Kapitel 1

## Motivation

Die numerische Simulation von physikalischen Zusammenhängen ist heute ein unentbehrliches Werkzeug für Wissenschaft und Wirtschaft, ist aber wohl eine der rechenintensivsten Anwendungen. Sie ermöglicht Experimente am Computer nachzustellen, die in der Praxis nur mit großem Aufwand oder gar nicht durchgeführt werden können.

Bei der numerischen Simulation werden die physikalischen Zusammenhänge zunächst in mathematischen Modellen erfasst. Diese sind im Allgemeinen nicht analytisch lösbar, und man beschränkt sich auf eine angenäherte Lösung an endlich vielen Punkten. Meist resultiert dies in sehr großen Gleichungssystemen, die entweder direkt oder iterativ gelöst werden müssen. Dies ist üblicherweise der für den Computer aufwendigste Teil einer Simulation, sodass durch dessen Optimierung Probleme schneller oder detaillierter behandelt werden können.

Diese Arbeit beschäftigt sich vorwiegend mit der Optimierung des Red-Black Gauss-Seidel-Verfahrens, das eine Vielzahl von linearen Gleichungssystemen iterativ lösen kann, auf zwei verbreiteten Prozessorarchitekturen. Dabei wird besonders auf in aktuellen Prozessoren verwirklichte Konzepte und ihre Folgen auf Auswahl und Anwendung der Optimierungstechniken eingegangen, um eine Übertragung auf ähnliche Algorithmen und folgende Prozessorgenerationen zu ermöglichen.

Für die Beschäftigung mit dem Red-Black Gauss-Seidel spricht nicht nur seine Vielseitigkeit und die Möglichkeit, ihn relativ einfach in Clustern zu parallelisieren. Er wird auch häufig bei Multi-Grid-Verfahren eingesetzt, die zu den schnellsten verfügbaren Lösungsverfahren zählen. Obwohl hierbei nur wenige Iterationen auf denselben Daten zum Glätten der Fehler notwendig sind, wird hierfür die meiste Zeit verwendet. [Wei01]

## Kapitel 2

# Modellproblem und Red-Black Gauss-Seidel

Als Modellproblem, um den Red-Black Gauss-Seidel implementieren und optimieren zu können, wurde für diese Arbeit die Poisson-Gleichung

$$\Delta\phi = f$$

gewählt, eine partielle Differentialgleichung zweiter Ordnung. Das aus der Gleichung folgende Randwertproblem kann viele physikalische Zusammenhänge beschreiben und ist deshalb im Bereich der Simulation häufig anzutreffen, z.B. bei der Berechnung von elektrischen und Gravitationsfeldern, sie modelliert aber auch die Verteilung und Auswirkung des Drucks bei Strömungen.  $\Delta$  ist hierbei der Laplace-Operator, der definiert ist als

$$\Delta = \sum_k \frac{\delta^2}{\delta x_k^2}$$

Um die Algorithmen und ihre Optimierung verstehen zu können, werden in diesem Kapitel zunächst die Grundlagen des Gauss-Seidel-Verfahrens vermittelt. Anschließend wird die Diskretisierung des Modellproblems im zwei- und dreidimensionalen Fall und die Anwendung des Gauss-Seidel-Verfahrens beschrieben. Zuletzt wird gezeigt, wie man vom allgemeinen Gauss-Seidel-Verfahren zum Red-Black Gauss-Seidel gelangt, und es werden einfache Implementierungen für den zwei- und dreidimensionalen Fall vorgestellt.

### 2.1 Gauss-Seidel-Verfahren

Das Gauss-Seidel-Verfahren kann zur Lösung von linearen Gleichungssystemen der Form

$$Ax = y$$

genutzt werden.

Dabei wird die Matrix  $A$  nun zerlegt in

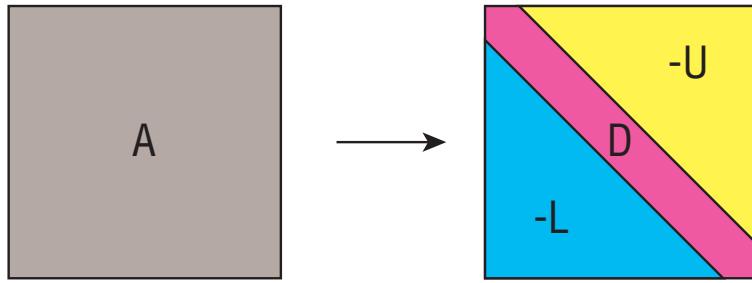

$$A = D - L - U$$

wobei  $D$  aus den Werten der Hauptdiagonalen besteht, und  $L$  und  $U$  eine linke und obere strenge Dreiecksmatrix sind (vgl. Abbildung 2.1).

Durch Einsetzen ergibt sich dann:

$$(D - L) \cdot x = U \cdot x + y$$

Abbildung 2.1: Zerlegung von  $A$  in  $D$ ,  $L$  und  $U$

Das daraus abgeleitete Iterationsverfahren

$$D \cdot x^{k+1} - L \cdot x^{k+1} = U \cdot x^k + y$$

lässt sich dann – da  $L$  und  $U$  Dreiecksmatrizen sind – auch darstellen als

$$d_{i,i} \cdot x_i^{k+1} - \sum_{j=1}^{i-1} l_{j,i} \cdot x_j^{k+1} = \sum_{j=i+1}^{i_{max}} u_{j,i} \cdot x_j^k + y_i$$

Da die Werte von  $D$ ,  $L$  und  $U$  aus  $A$  entstanden sind, entspricht dies

$$x_i^{k+1} = \frac{\sum_{j=1}^{i-1} -a_{j,i} \cdot x_j^{k+1} + \sum_{j=i+1}^{i_{max}} -a_{j,i} \cdot x_j^k + y_i}{a_{i,i}}$$

Auf eine genaue Untersuchung, wann und wie schnell das Verfahren konvergiert, wird hier verzichtet und auf die einschlägige Literatur der Linearen Algebra verwiesen. Das Gauss-Seidel-Verfahren ist allgemein anwendbar und konvergiert, wenn die Matrix  $A$  positiv definit oder streng diagonal dominant ist.

Die Iterationsregel lässt sich nun folgendermaßen interpretieren: Ausgehend von einer beliebigen Anfangslösung  $x^0$  werden die Näherungen  $x^1$  bis  $x^n$  berechnet. Zumindest im allgemeinen Fall beginnt jeder Iterationsschritt mit der Berechnung von  $x_1^{k+1}$ , da dieses ausschließlich von Werten aus  $x^k$  abhängt. Danach können sukzessive  $x_2^{k+1}$ , das von  $x_1^{k+1}$  abhängen kann, bis  $x_{i_{max}}^{k+1}$  berechnet werden. Wirklich effizient ist dieses Verfahren allerdings nur, wenn  $A$  dünn besetzt ist, und dies auch zur Reduzierung der Berechnungen genutzt werden kann. Meist kennt man allerdings die Struktur des Gleichungssystems und muss es nicht explizit aufstellen. Die Berechnung eines neuen Wertes  $x_i^{k+1}$  entspricht nichts anderem, als die Einzelgleichung, die zu Zeile  $i$  in  $A$  geführt hat, lokal zu lösen; dafür werden sowohl die in der aktuellen Iteration schon berechneten Werte  $x_1^{k+1}$  bis  $x_{i-1}^{k+1}$ , als auch  $x_i^k$  bis  $x_{i_{max}}^k$  aus der vorhergehenden verwendet.

## 2.2 Diskretisierung der Poisson-Gleichung

Zur iterativen Lösung der Poisson-Gleichung

$$\Delta\phi = f$$

mit Randwertbedingungen

$$\phi(\vec{x}) = \Gamma(\vec{x}) \quad \forall \vec{x} \in \delta\Omega$$

muss diese zunächst auf einem Gitter diskretisiert werden.

Es wird hier davon ausgegangen, dass  $\Omega$  rechtwinklig begrenzt ist, also im Zweidimensionalen rechteckig und im Dreidimensionalen quaderförmig ist. Des weiteren soll eine Diskretisierung auf einem regelmäßigen Gitter möglich sein, die Größe von Omega muss dafür in jeder Dimension ein Vielfaches vom Gitterabstand  $dh$  sein.

### 2.2.1 2D Fall

Die zweidimensionale Poissons-Gleichung

$$\frac{\delta^2}{\delta x^2} \phi(x, y) + \frac{\delta^2}{\delta y^2} \phi(x, y) = f(x, y)$$

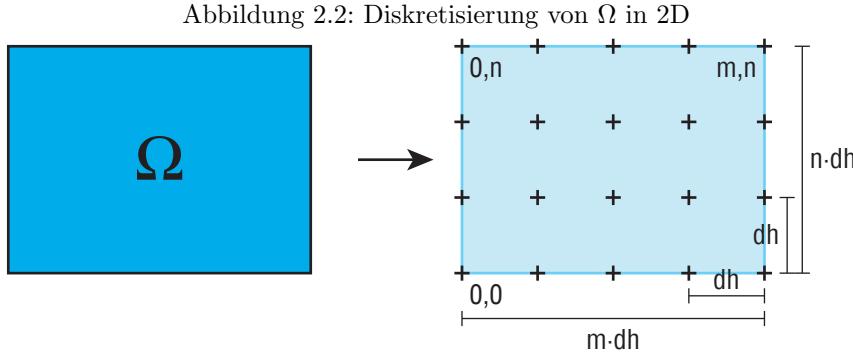

wird auf dem Gitter der Größe  $m \cdot dh$  in x-Richtung und  $n \cdot dh$  in y-Richtung diskretisiert. Es entstehen die Werte  $U(i, j)$  mit  $i = 0..m$  und  $j = 0..n$  aus  $\phi$  und aus  $f$  die Werte  $F(i, j)$  mit  $i = 1..m - 1$  und  $j = 1..n - 1$ . Die Werte  $U(i, j)$  enthalten für  $i = 0 \vee i = m \vee j = 0 \vee j = n$  die diskretisierten Randwerte (vgl. Abbildung 2.2).

Die Ableitungen zweiter Ordnung für den Laplace-Operator können durch die Methode der Finiten Differenzen im diskreten Fall angenähert werden:

Die Addition der Taylor-Reihen

$$\phi(x + h, y) = \phi(x, y) + h \cdot \frac{\delta}{\delta x} \phi(x, y) + h^2 \cdot \frac{\delta^2}{\delta x^2} \phi(x, y) + h^3 \cdot \frac{\delta^3}{\delta x^3} \phi(x, y) + \mathcal{O}(h^4)$$

$$\phi(x - h, y) = \phi(x, y) - h \cdot \frac{\delta}{\delta x} \phi(x, y) + h^2 \cdot \frac{\delta^2}{\delta x^2} \phi(x, y) - h^3 \cdot \frac{\delta^3}{\delta x^3} \phi(x, y) + \mathcal{O}(h^4)$$

ergibt dann nach Division der Summe durch  $h^2$ :

$$\frac{\phi(x - h, y) - 2 \cdot \phi(x, y) + \phi(x + h, y)}{h^2} = \frac{\delta^2}{\delta x^2} \phi(x, y) + \mathcal{O}(h^2)$$

und analog

$$\frac{\phi(x, y - h) - 2 \cdot \phi(x, y) + \phi(x, y + h)}{h^2} = \frac{\delta^2}{\delta y^2} \phi(x, y) + \mathcal{O}(h^2)$$

Der zweidimensionale Laplace-Operator kann dann angenähert werden durch

$$\Delta^{*}_{2D} = \frac{\phi(x - h, y) - 2 \cdot \phi(x, y) + \phi(x + h, y)}{h^2} + \frac{\phi(x, y - h) - 2 \cdot \phi(x, y) + \phi(x, y + h)}{h^2}$$

Setzt man  $h = dh$  und vernachlässigt die Diskretisierungsfehler, ergibt sich das lineare Gleichungssystem

$$\frac{U(i - 1, j) - 2 \cdot U(i, j) + U(i + 1, j)}{dh^2} + \frac{U(i, j - 1) - 2 \cdot U(i, j) + U(i, j + 1)}{dh^2} = F(i, j)$$

oder anders ausgedrückt

$$U(i, j) = \frac{1}{4} \cdot [U(i + 1, j) + U(i - 1, j) + U(i, j + 1) + U(i, j - 1) - dh^2 \cdot F(i, j)] \quad 0 < i < m, 0 < j < n$$

Das Gleichungssystem lässt sich in Matrixschreibweise darstellen als

$$Ax = y$$

wobei  $A$  eine Matrix der Größe  $((m-1) \cdot (n-1)) \times ((m-1) \cdot (n-1))$  ist.  $A$ ,  $x$  und  $y$  können zum Beispiel folgendermaßen belegt sein:

$$x = \begin{pmatrix} U(1, 1) \\ \vdots \\ U(m-1, 1) \\ U(1, 2) \\ \vdots \\ \vdots \\ U(m-1, n-1) \end{pmatrix}$$

$x$  enthält somit die sortierten Unbekannten von  $U$ .

$$A = \begin{pmatrix} A_1 & I & & \\ I & A_2 & I & \\ & I & \ddots & \ddots & \\ & & \ddots & \ddots & I \\ & & & I & A_{n-1} \end{pmatrix} \text{ mit } A_n = \begin{pmatrix} -4 & 1 & & \\ 1 & -4 & 1 & \\ & 1 & \ddots & \ddots & \\ & & \ddots & \ddots & 1 \\ & & & 1 & -4 \end{pmatrix}$$

Die  $I$  sind Einheitsmatrizen, die ebenso wie die  $A_n$  die Größe  $(m-1) \times (m-1)$  besitzen. Die Werte auf der Hauptdiagonalen sind ausschließlich  $-4$ , die restlichen Werte  $a_{i,j}$  sind dort 1, wo  $x_j$  ein Nachbar des durch  $x_i$  spezifizierten  $U$  sind, sonst 0.

$$y = \begin{pmatrix} F(1, 1) - r_1(1, 1) - r_2(1, 1) \\ \vdots \\ F(m-1, 1) - r_1(m-1, 1) - r_2(m-1, 1) \\ \vdots \\ \vdots \\ F(m-1, n-1) - r_1(m-1, n-1) - r_2(m-1, n-1) \end{pmatrix}$$

mit  $r_1(i, j) = \begin{cases} U(0, j) & \text{für } i = 1 \\ U(m, j) & \text{für } i = m-1 \\ 0 & \text{sonst} \end{cases}$

und  $r_2(i, j) = \begin{cases} U(i, 0) & \text{für } j = 1 \\ U(i, n) & \text{für } j = n-1 \\ 0 & \text{sonst} \end{cases}$

$y$  besteht aus den wie die  $U$  in  $x$  sortierten diskretisierten Werten aus  $F$ , wobei bei Werten am Rand die anliegenden Randwerte abgezogen werden müssen.

### 2.2.2 3D Fall

Mit ausgeschriebenem Laplace-Operator lautet die Poisson-Gleichung im dreidimensionalen Fall

$$\frac{\delta^2}{\delta x^2} \phi(x, y, z) + \frac{\delta^2}{\delta y^2} \phi(x, y, z) + \frac{\delta^2}{\delta z^2} \phi(x, y, z) = f(x, y, z)$$

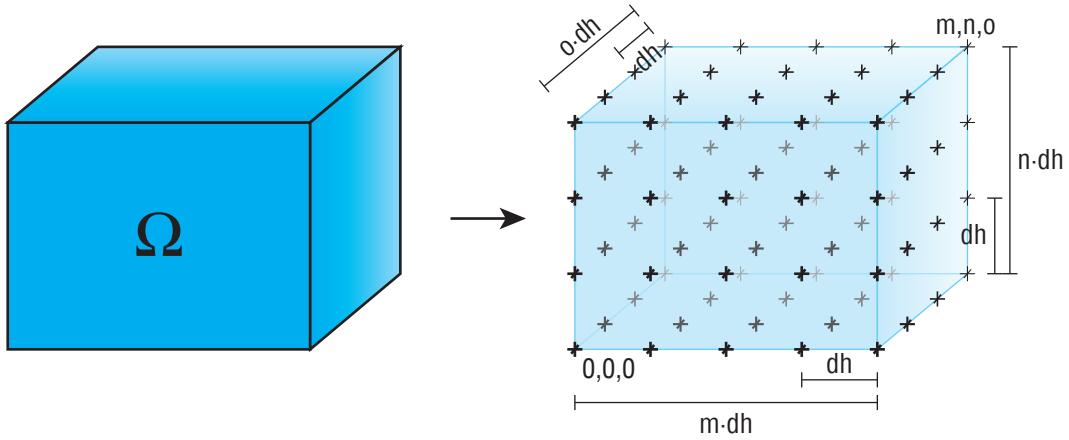

Die Diskretisierung wird analog zum zweidimensionalen Fall durchgeführt (vgl. Abbildung 2.3) und es entstehen aus  $\phi$  die Werte  $U(i, j, k)$  mit  $i = 0..m$ ,  $j = 0..n$ ,  $k = 0..o$  und  $F(i, j, k)$  mit  $i = 1..m-1$ ,  $j = 1..n-1$  und  $k = 1..o-1$ .

Abbildung 2.3: Diskretisierung von  $\Omega$  in 3D

Auch der diskretisierte dreidimensionale Laplace-Operator kann analog angenähert werden, indem die Finiten Differenzen auch in z-Richtung gebildet und eingesetzt werden.

$$\Delta^*_{3D} = \frac{\phi(x-h, y, z) - 2 \cdot \phi(x, y, z) + \phi(x+h, y, z)}{h^2} \\ + \frac{\phi(x, y-h, z) - 2 \cdot \phi(x, y, z) + \phi(x, y+h, z)}{h^2} \\ + \frac{\phi(x, y, z-h) - 2 \cdot \phi(x, y, z) + \phi(x, y, z+h)}{h^2}$$

Das Gleichungssystem ergibt sich dann zu

$$F(i, j, k) = \frac{U(i-1, j, k) - 2 \cdot U(i, j, k) + U(i+1, j, k)}{dh^2} \\ + \frac{U(i, j-1, k) - 2 \cdot U(i, j, k) + U(i, j+1, k)}{dh^2} \\ + \frac{U(i, j, k-1) - 2 \cdot U(i, j, k) + U(i, j, k+1)}{dh^2}$$

oder

$$U(i, j, k) = \frac{1}{6} \cdot [U(i+1, j, k) + U(i-1, j, k) + U(i, j+1, k) + U(i, j-1, k) \\ + U(i, j, k+1) + U(i, j, k-1) - dh^2 \cdot F(i, j, k)]$$

mit  $0 < i < m$ ,  $0 < j < n$ ,  $0 < k < o$

Die Matrixgleichung  $Ax = y$  lässt sich dann aufstellen mit

$$A = \begin{pmatrix} A_1^{2D} & I & & & \\ I & A_2^{2D} & I & & \\ & I & \ddots & \ddots & \\ & & \ddots & \ddots & I \\ & & & I & A_{o-1}^{2D} \end{pmatrix}$$

Die  $A_n^{2D}$  entsprechen einer Matrix  $A$  aus dem zweidimensionalen Fall mit  $m_{2D} := m_{3D}$  und  $n_{2D} := n_{3D}$ .

$$x = \begin{pmatrix} U(1, 1, 1) \\ \vdots \\ U(m, 1, 1) \\ U(1, 2, 1) \\ \vdots \\ U(m, n, 1) \\ U(1, 1, 2) \\ \vdots \\ U(m - 1, n - 1, o - 1) \end{pmatrix}$$

$y$  enthält – wie im zweidimensionalen Fall – die diskretisierten Werte aus  $F$  in derselben Sortierung wie die  $U$  in  $x$ , wobei an den Ecken, Kanten und Seiten die anliegenden Randwerte abgezogen werden müssen.

### 2.3 Anwendung auf das Modellproblem und Variante des Red-Black Gauss-Seidel

Der Beweis, dass die durch die oben beschriebenen Verfahren erzeugten  $A$  positiv definit sind, kann z. B. in [Hac93] nachgelesen werden.

Bei der Implementierung des Gauss-Seidel-Verfahrens ist es nicht nötig, das Gleichungssystem tatsächlich explizit aufzustellen. Entscheidend ist nur, die neuen Werte von  $U$  in der Reihenfolge im gedachten  $x$  neu zu berechnen. Da nach seiner Berechnung in  $U^{k+1}$  der Wert aus  $U^k$  nicht mehr benötigt wird, kann dieser im Speicher überschrieben werden.

Beim normalen Gauss-Seidel-Verfahren wird die Matrix-Gleichung wie in den Abschnitten 2.2.1 und 2.2.2 zugrunde gelegt. Die damit zusammenhängende Abarbeitungsreihenfolge beginnt zunächst mit der Berechnung eines neuen  $U(1, 1)$  bzw.  $U(1, 1, 1)$  und fährt dann mit  $U(2, 1)$  bzw.  $U(2, 1, 1)$  die ganze Zeile bis  $U(m - 1, 1)$  bzw.  $(m - 1, 1, 1)$  hindurch fort. Anschließend wird die Zeile  $U(x, 2)$  bzw.  $U(x, 2, 1)$  berechnet und so weiter, bis im zweidimensionalen Fall das ganze Gitter oder in 3D eine ganze Ebene fertiggestellt ist. Im dreidimensionalen Fall wird dann Ebene für Ebene ebenso verfahren.

Dem Red-Black Gauss-Seidel liegt gedanklich eine andere Sortierung der Werte  $U$  in  $x$  zugrunde. Hierzu wird das Innere des Gitters  $U$  schachbrettartig in sogenannte rote und schwarze Punkte aufgeteilt, wobei für den zweidimensionalen Fall üblicherweise gilt

$$U(i, j) = \begin{cases} \text{rot für } (i + j) \bmod 2 = 0 \\ \text{schwarz für } (i + j) \bmod 2 = 1 \end{cases}$$

und im dreidimensionalen

$$U(i, j, k) = \begin{cases} \text{rot für } (i + j + k) \bmod 2 = 1 \\ \text{schwarz für } (i + j + k) \bmod 2 = 0 \end{cases}$$

Die Reihenfolge der Berechnungen entspricht einer Matrixgleichung, bei der  $x_1$  bis  $x_i$  nur roten und  $x_{i+1}$  bis  $x_{i_{max}}$  nur schwarzen Punkten entspricht. In diesem Fall hängen die ersten  $i$  roten Werte ausschließlich von schwarzen Werten aus  $x^k$  ab, die folgenden schwarzen Werte ausschließlich von roten Werten aus  $x^{k+1}$ . Eine Iteration teilt sich damit in eine rote und eine schwarze Halbiteration auf. Für eine Implementierung kann vorteilhaft sein, dass die Berechnungen innerhalb einer Halbiterationen voneinander unabhängig sind und in beliebiger Reihenfolge oder parallel abgearbeitet werden können.

Der Red-Black Gauss-Seidel ist demnach nur eine bestimmte Methode, das Gauss-Seidel-Verfahren anzuwenden. Während beim Modellproblem das Gitter in zwei „Farben“ aufgeteilt werden kann, so kann im Allgemeinen eine Aufteilung nur mit mehreren Gruppen oder gar nicht erreicht werden.

## 2.4 Implementierung

Die beschriebenen Gauss-Seidel-Verfahren lassen sehr direkt implementieren. Die auf dem Gitter diskretisierten Werte  $U$  und  $F$  werden dazu in mehrdimensionalen Arrays gespeichert.

In der Praxis wird man die Größe von  $F$  genauso wählen wie die von  $U$ . Denn zum einen unterstützen viele Programmiersprachen keine beliebigen Arraygrenzen, zum anderen erleichtert dies dem Compiler die Adressberechnung; der für eine Berechnung benötigte Wert aus  $F$  und ihr Ziel in  $U$  haben damit nämlich dieselbe Adresse relativ zum Anfang der Arrays.

### beispielhafte Implementation des 2D-Gauss-Seidel

---

```

#Arrays der benötigten Größe anlegen

alloc array U[0..m;0..n]

alloc array F[1..m-1;1..n-1]

#diskrete Werte auf dem Gitter in U und F berechnen

call init

#gewünschte Anzahl an Gauss-Seidel-Iterationen ausführen

repeat number of iterations times

for j=1..(n-1)

for i=1..(m-1)

U[i;j]=( U[i-1;j]+U[i+1;j]+U[i;j-1]+U[i;j+1] \

-dh*dh*F[i;j] )/4.0

next i

next j

end repeat

```

---

### beispielhafte Implementation des 3D-Gauss-Seidel

---

```

#Arrays der benötigten Größe anlegen

alloc array U[0..m;0..n;0..o]

alloc array F[1..m-1;1..n-1;1..o-1]

#diskrete Werte auf dem Gitter in U und F berechnen

call init

#gewünschte Anzahl an Gauss-Seidel-Iterationen ausführen

repeat number of iterations times

for k=1..(o-1)

for j=1..(n-1)

for i=1..(m-1)

U[i;j]=( U[i-1;j;k]+U[i+1;j;k]+U[i;j-1;k] \

+U[i;j+1;k]+U[i;j;k-1]+U[i;j;k+1] \

-dh*dh*F[i;j] )/6.0

next i

next j

next k

end repeat

```

---

## **beispielhafte Implementation des 2D-Red-Black-Gauss-Seidel**

---

```

#Arrays der benötigten Größe anlegen

alloc array U[0..m;0..n]

alloc array F[1..m-1;1..n-1]

#diskrete Werte auf dem Gitter in U und F berechnen

call init

#gewünschte Anzahl an Gauss-Seidel-Iterationen ausführen

repeat number of iterations times

# rote Halbiteration

for j=1..(n-1)

for i=1..(m-1)

if ( (i+j) mod 2 = 0) then

U[i;j]=( U[i-1;j]+U[i+1;j]+U[i;j-1]+U[i;j+1] \

-dh*dh*F[i;j] )/4.0

fi

next i

next j

# schwarze Halbiteration

for j=1..(n-1)

for i=1..(m-1)

if ( (i+j) mod 2 = 1) then

U[i;j]=( U[i-1;j]+U[i+1;j]+U[i;j-1]+U[i;j+1] \

-dh*dh*F[i;j] )/4.0

fi

next i

next j

end repeat

```

---

### beispielhafte Implementation des 3D-Red-Black-Gauss-Seidel

---

```

#Arrays der benötigten Größe anlegen

alloc array U[0..m;0..n,0..o]

alloc array F[1..m-1;1..n-1;1..o-1]

#diskrete Werte auf dem Gitter in U und F berechnen

call init

#gewünschte Anzahl an Gauss-Seidel-Iterationen ausführen

repeat number of iterations times

# rote Halbiteration

for k=1..(o-1)

for j=1..(n-1)

for i=1..(m-1)

if ( (i+j+k) mod 2 = 1) then

U[i;j;k]=( U[i-1;j;k]+U[i+1;j;k]+U[i;j-1;k] \

+U[i;j+1;k]+U[i;j;k-1]+U[i;j;k+1] \

-dh*dh*F[i;j;k] )/6.0

fi

next i

next j

next k

# schwarze Halbiteration

for k=1..(o-1)

for j=1..(n-1)

for i=1..(m-1)

if ( (i+j+k) mod 2 = 0) then

U[i;j;k]=( U[i-1;j;k]+U[i+1;j;k]+U[i;j-1;k] \

+U[i;j+1;k]+U[i;j;k-1]+U[i;j;k+1] \

-dh*dh*F[i;j;k] )/6.0

fi

next i

next j

next k

end repeat

```

---

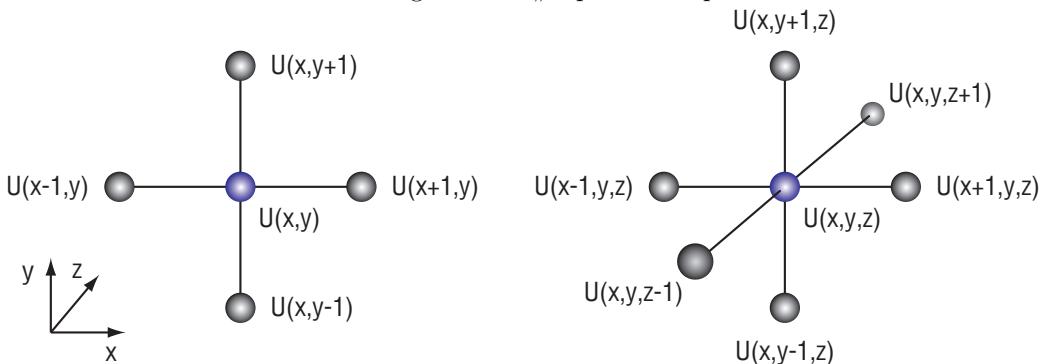

Aufgrund seiner „Form“ wird der für die Berechnung neuer Werte benötigte, durch Finite Differenzen angenäherte, diskrete Laplace-Operator häufig als 5-Punkt- im zweidimensionalen bzw. 7-Punkt-Stempel im dreidimensionalen Fall bezeichnet (vgl. Abbildung 2.4).

Abbildung 2.4: Der „Laplace-Stempel“

Da man die beschriebenen Verfahren sowohl aus einer mathematischen als auch rein algorithmischen Sicht betrachten kann, sollte noch auf die unterschiedliche Verwendung bestimmter Begriffe und Bezeichnungen hingewiesen werden. Insbesondere ist der Begriff der Größe eines Problems nicht eindeutig. Geht man von einer diskretisierten partiellen Differentialgleichung aus, wird man die Problemgröße an  $\Omega$  festmachen und von einem  $m \times n$  bzw.  $m \times n \times o$  großen Problem sprechen. Ausgehend von einer rein algorithmischen oder allgemein auf das Lösen von Gleichungssystemen bezogenen Sicht ist dasselbe Problem allerdings  $(m-1) \times (n-1)$  bzw.  $(m-1) \times (n-1) \times (o-1)$  groß, da dies die Menge der Unbekannten darstellt. In dieser Arbeit wird die letztere Art der Bezeichnung bevorzugt.

Zum anderen ist es üblich, sich auf die Nachbarn des Wertes  $U_{i,j}$  bzw.  $U_{i,j,k}$  der Einfachheit halber über eine Form von Richtungsangabe zu beziehen, wobei sich hier keine eindeutige und für zwei- und dreidimensionale Gitter einheitliche Bezeichnung durchgesetzt hat. In dieser Arbeit werden die Dimensionen mit der üblichen Vorstellung von programmiersprachlichen mehrdimensionalen Feldern im Speicher assoziiert. Somit gilt:  $U_{x+1,y}$  rechts von  $U_{x,y}$ ,  $U_{x,y+1}$  unter  $U_{x,y}$  und im Dreidimensionalen  $U_{x,y,z+1}$  hinter  $U_{x,y,z}$ .

# Kapitel 3

## Wichtige Konzepte zur Steigerung der Prozessorleistung

Während es durch die Verbesserung der Fertigungsverfahren von Halbleitern möglich ist, immer mehr Schaltungen auf kleinerem Raum unterzubringen, so verdanken moderne Prozessoren ihre hohe Geschwindigkeit viel mehr Konzepte, die die dadurch mögliche höhere Komplexität effektiv in schnellere Verarbeitung verwandeln.

Zudem werden Hauptspeicher zwar immer größer, doch konnte ihre Fähigkeit, den Prozessor auch rechtzeitig und ausreichend mit Daten zu versorgen, nicht entsprechend gesteigert werden. Deshalb wurden verschiedene Methoden entwickelt, um die großen Rechenkapazitäten besser zu nutzen.

In diesem Kapitel sollen einige dieser Konzepte und Methoden vorgestellt werden, die für das Verständnis von Optimierungstechniken notwendig sind. Deren Kenntnis wird bei der Vorstellung der Testsysteme im folgenden Kapitel vorausgesetzt.

### 3.1 Erhöhung des Instruktionsdurchsatzes

#### 3.1.1 Pipelining und Superpipelining

Die Abarbeitung einer Instruktion umfasst im allgemeinen Laden und Dekodieren der Instruktion, Laden der Operanden, Ausführung der Operation und Schreiben des Ergebnisses. Beim Fließbandverfahren (*Pipelining*) beginnt die Abarbeitung der nächsten Operation bereits, wenn der erste Schritt der Abarbeitung des vorhergehenden Befehls beendet ist. Im Idealfall findet auf jeder Stufe der Pipeline die Teilverarbeitung jeweils verschiedener Instruktionen gleichzeitig statt.

Es besteht auch die Möglichkeit, diese Stufen der Pipeline noch feiner zu granulieren; die Schaltungen für den einzelnen Bearbeitungsschritt werden damit weniger komplex und können dadurch mit einer höheren Taktfrequenz betrieben werden. Dies wird als *Superpipelining* bezeichnet.

Pipelining und Superpipelining führen damit nicht einzelne Befehle schneller aus, sondern ermöglichen durch eine gewisse Parallelität unter günstigen Umständen einen deutlich höheren Instruktionsdurchsatz. Sind für einen Befehl allerdings die Operanden nicht rechtzeitig vorhanden (weil sie aus unteren Speicherebene geladen werden oder von anderen in der Pipeline befindlichen Operationen abhängen), müssen Teile des Fließbandes vorübergehend angehalten werden (*Pipeline Stalls*). Noch gravierender ist das Problem bei bedingten Sprüngen, da hier erst dann der nächste Befehl geholt werden kann, wenn diese Instruktion vollständig abgearbeitet und damit das Sprungziel bekannt ist.

### 3.1.2 Speculative Execution

Da bei bedingten Sprüngen die Pipeline einmal vollständig geleert wird, verliert Pipelining bei kurzen Schleifen oder verschachtelten Kontrollstrukturen seine große Effizienz. Deshalb ist man dazu übergegangen, bei bedingten Sprüngen einen Entscheidungszweig zunächst „auf Verdacht“ zu bearbeiten (*Speculative Execution*). Allerdings: Wenn der falsche Zweig gewählt wurde, müssen die begonnenen Berechnungen in der Pipeline verworfen, und es muss mit den richtigen Instruktionen neu begonnen werden.

Meist ist entweder spezifiziert, bei welchen Befehlen welcher Zweig bevorzugt wird, oder es existieren mehrere Instruktionsvarianten, bei denen jeweils ein bestimmter Zweig spekulativ ausgeführt wird. Auf jeden Fall müssen Compiler oder Programmierer dies bei der Code-Generierung beachten, um eine möglichst schnelle Ausführung zu ermöglichen.

Auch eine Einheit zum Voraussagen der Sprungziele (*Branch Prediction*) ist üblich, die bei mehrfacher Ausführung den statistisch wahrscheinlicheren Zweig ermittelt.

Der Vollständigkeit halber sollte eine spezielle Form der Branch Prediction erwähnt werden, die häufig bei Unterfunktionsaufrufen angewendet wird: Während „return“-Anweisungen immer Sprünge ausführen, hängt dieses von der im Stapel gespeicherten Rücksprungadresse ab. Die letzten Rücksprungadressen werden zur schnellere Verfügbarkeit in einem Puffer gespeichert. Da die Rücksprungadresse, obwohl schlechter Programmierstil, im Stapspeicher geändert worden sein kann, muss der Sprung auf die gepufferte Adresse zunächst spekulativ ausgeführt werden.

### 3.1.3 Out of Order Execution

Um auch Verzögerung durch noch nicht verfügbare Operatoren zu reduzieren, können moderne Prozessoren auch die Abarbeitung von Instruktionen vorziehen, deren Operatoren bereits verfügbar sind (*Out of Order Execution*).

Hierbei werden die ursprünglichen Maschinensprachebefehle nach dem Dekodieren zunächst in eine Warteschlange gestellt. Ein Scheduler wählt hieraus Instruktionen, deren Operanden vorhanden sind und für die er eine Abhängigkeit mit laufenden Instruktionen ausschließen kann. Diese übergibt er dann den dafür vorgesehenen Recheneinheiten. Nach Ende der Berechnung muss allerdings sichergestellt werden, dass die Instruktionen in ihrer logischen Reihenfolge wirksam werden (*Retirement*).

Die Möglichkeiten des Schedulers werden dadurch weiter unterstützt, dass entgegen der Programmierer-Sicht eine größere Anzahl von Registern vorhanden (*Register File*) ist. So können voneinander unabhängige, aber für dasselbe Register vorgesehene Instruktionen parallel ausgeführt werden. Dieses Verfahren kann Daten-Abhängigkeiten, die nur scheinbar wegen der geringen Registeranzahl bestehen, bei der Programmausführung beseitigen und wird als *Register Renaming* bezeichnet.

### 3.1.4 Superscalarity

Superskalare Prozessoren beinhalten für jede Operationsart nicht nur eine, sondern mehrere Recheneinheiten. Bei entsprechender Versorgung mit Instruktionen und Operanden und dem Fehlen von Abhängigkeiten kann der Scheduler dadurch in einem Takt die Berechnung mehrerer Instruktionen gleichzeitig starten. Superskalare Prozessoren sind damit in der Lage, effektiv mehr als eine Operation pro Takt auszuführen.

### 3.1.5 Chaining

Unter *Chaining* versteht man Verfahren, die die Verfügbarkeit benötigter Operanden beschleunigen. Muss eine Instruktion z. B. auf das Ergebnis einer laufenden Berechnung warten, kann dieses sofort nach Abschluss der Berechnung, aber noch vor Retirement und Ausschreiben in Register oder den Hauptspeicher, genutzt werden.

### 3.1.6 SIMD

Insbesondere bei mathematischen Anwendungen wird dieselbe Operationen auf eine große Menge von gleichartigen Daten angewendet. Bereits um 1960 starteten die ersten Versuche zur Entwicklung von Vektorrechnern, die, anstatt dieselbe Operation immer wieder auf die verschiedenen Werte (Skalare) anzuwenden (Single Instruction Single Data, SISD), dieselbe Operation auf ein ganzes Array mehrerer gleichartiger Werte (Vektor) ausführten (Single Instruction Multiple Data, SIMD).

Mittlerweile sind reine Vektorprozessoren unüblich – meist lässt sich dieselbe Leistung mit Clustern aus üblichen Allzweck-Prozessoren günstiger erreichen. Dennoch hat dieses Konzept zunächst als Vektor-Koprozessoren, später aber auch als in den Prozessor integrierte Vektor- oder SIMD-Einheiten Einzug gefunden.

Die heute üblichen SIMD-Einheiten können Vektoren von bis zu 128 Bit Größe verarbeiten, also z. B. Berechnungen auf vier Fließkommazahlen einfacher Genauigkeit oder logische und arithmetische Operationen auf 1 Byte-Werte ausführen. Dies bietet Vorteile gegenüber einer superskalaren Berechnung: Es muss nur ein Befehl dekodiert und bei Operanden im Speicher nur eine Adresse berechnet werden. Außerdem können diese Vektoreinheiten auch selbst superskalar ausgeführt sein.

## 3.2 Erhöhung des Speicherdurchsatzes

### 3.2.1 Caches

Eine der ersten Maßnahmen, die Kluft zwischen dem Bedarf des Prozessors an Instruktionen und Daten auf der einen Seite und der Möglichkeit des Hauptspeichers, diesen auch zu erfüllen, andererseits zu verringern, war die Einführung von Zwischenspeichern (*Caches*) oder Hierarchien von Caches.

Einzelne Caches lassen sich zunächst wie Hauptspeicher durch äußere Eigenschaften wie ihre Größe, ihre Latenz und Bandbreite charakterisieren. Die Latenz entspricht hierbei der Zeit oder der Zahl an Taktzyklen, bis Lese- oder Schreibanfragen erfüllt werden. Die Bandbreite gibt an, welche Datenmenge nach der Latenzzeit dauerhaft übertragen werden kann. Angewandt auf einzelne Algorithmen wird allerdings auch entscheidend, welchen Kompromiss der Hersteller bei Cache-Zeilen-Länge und Assoziativität gewählt hat: Größere Cache-Zeilen benötigen weniger Logik zur Verwaltung und ermöglichen bessere Nutzung lokaler Nähe bei benachbarten Speicherzugriffen, erhöhen den tatsächlichen Speicherbedarf aber bei weit verstreuten und einmaligen Zugriffen. Auch höhere Assoziativität kann wegen des steigenden Organisationsbedarfs oft nur auf Kosten der Geschwindigkeit erreicht werden. Zu beachten sind auch die Verdrängungsstrategie und das Verhalten bei Schreiboperationen, also ob die Konsistenz mit der darunter liegenden Specherebene sofort (*Write-Through*) oder erst bei Verdrängung (*Write-Back*) hergestellt wird.

Insgesamt muss noch die Zusammensetzung der Speicherhierarchie beachtet werden. So ist es heute üblich, auf den unteren Cache-Ebenen Daten für Instruktionen und Operanden gleich zu behandeln (*Unified*), aber zumindest in der höchsten Cacheebene getrennte Caches zu verwenden (*Instruction* und *Data Cache*). Durch der Zugriff auf den Hauptspeicher selbst kann durch die Verwendung von Caches beschleunigt werden: Moderner SD-RAM erreicht seinen höchsten Datentransfer bei größeren, aneinander hängenden Speicherblöcken (*Burst Mode*). Dies kann zum schnellen Füllen oder Ausschreiben der Cache-Zeilen genutzt werden, welche dieser Beschränkung nicht unterliegen.

### 3.2.2 Prefetching

Während Caches Latenz und Bandbreite bei Nutzung von temporaler und lokaler Nähe deutlich verbessern können, so können sie die Latenz bei Zugriffen auf bisher nicht in Caches vorhandene Speicherbereiche bestenfalls nicht verschlechtern. Es wäre deshalb wünschenswert, wenn Daten sich bereits in einem der Caches befinden, wenn sie tatsächlich von einer Instruktion angefordert werden.

Hierzu werden spezielle Einheiten im oder am Prozessor placiert, die Daten nach Möglichkeit vor ihrer tatsächlichen Anforderung in die Cache-Hierarchie laden (*Hardware Prefetcher*).

Hardware-Prefetcher für Instruktionen sind die einfachere und ältere Variante, da sie nur einem klar definierten und voraussehbaren Lesestrom folgen müssen. Moderne Instruktions-Prefetcher können auch spekulativ zusammen mit einer Branch Prediction arbeiten.

Hardware-Prefetcher für Operanden sind komplexer und können anhand einer Analyse der Speicher-Zugriffsmuster eines laufenden Programmes nur vermutlich benötigte Daten voraussagen. Im Allgemeinen können sie nur eine begrenzte Anzahl kontinuierlicher Lese- und Schreibströme erkennen.

Oft besteht auch die Möglichkeit, über spezielle Maschinensprachebefehle Daten in die Caches zu laden oder das Verhalten der Hardware-Prefetcher zu beeinflussen.

### 3.2.3 Write Combining

Die Organisation der Caches in Zeilen kann insbesondere bei Schreiboperationen zu Geschwindigkeitsverlust führen. Werden einzelne Werte geschrieben und sollen in einem Cache eingelagert werden, muss die gesamte Zeile aus dem Speicher geladen und entsprechend im Cache kombiniert werden. Über *Write Combining Buffer* können aufeinander folgende Schreibzugriffe gesammelt werden. Wenn der Inhalt eines Puffer den kompletten Inhalt einer Cache-Zeile fällt, müssen keine Werte aus dem Hauptspeicher mehr gelesen werden. Bei Multiprozessor- oder zumindest -tauglichen Systemen sind hier dennoch Maßnahmen zur Synchronisation notwendig, damit keine anderen Einheiten veraltete Daten aus dem Speicher laden. Besonders effizient ist dieses Verfahren, wenn Daten sequentiell geschrieben werden, und die Anzahl der Schreibströme die Anzahl der Write Combining Buffer nicht übersteigt.

# Kapitel 4

## Vorstellung der Test-Systeme

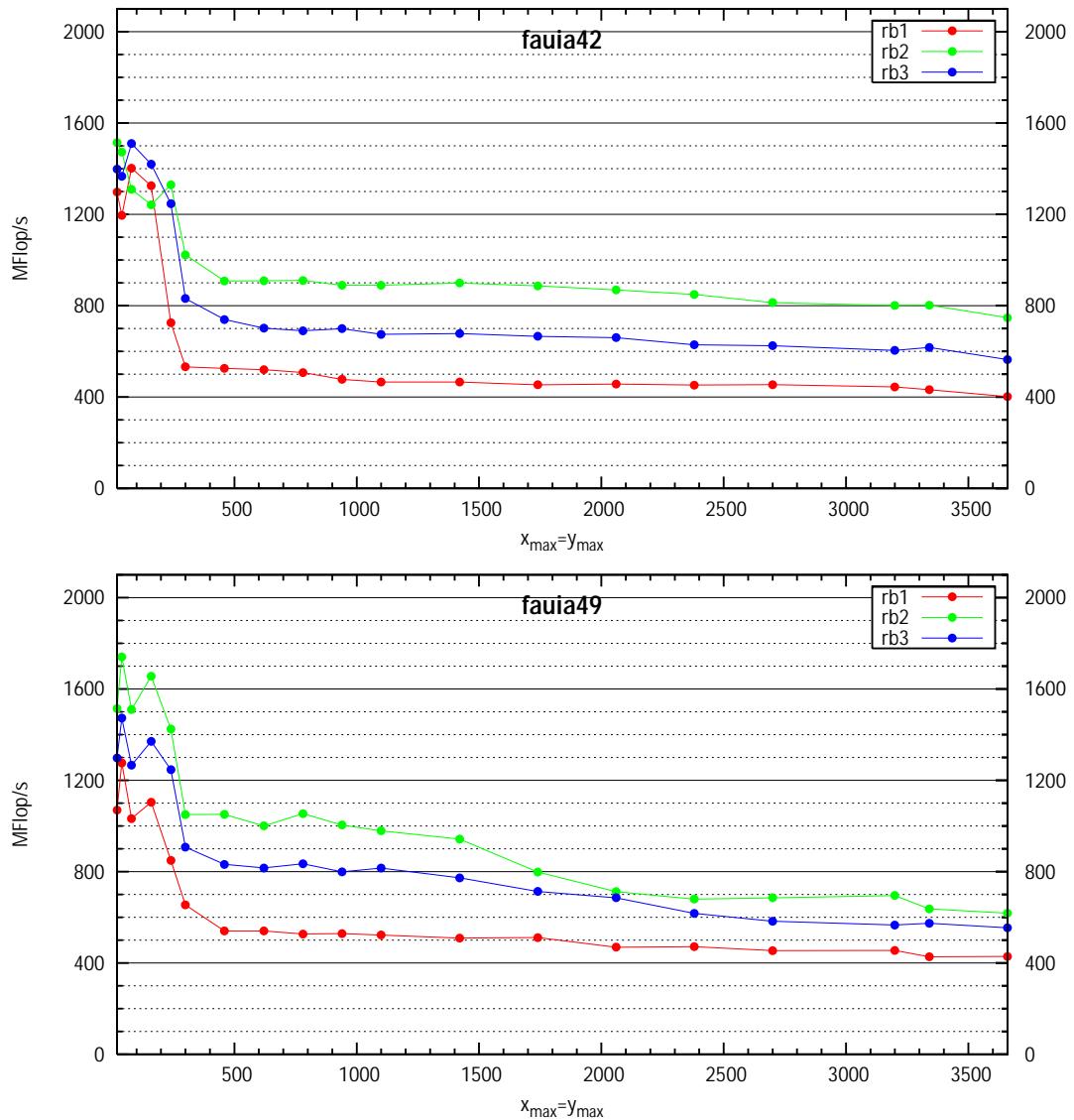

### 4.1 Intel Pentium 4 Prescott 3,2 GHz [fauia42.informatik.uni-erlangen.de](http://fauia42.informatik.uni-erlangen.de)

Intel bezeichnet mit „Pentium 4 Prozessor“ eigentlich keinen Prozessor, sondern eine ganze Prozessorfamilie zum Einsatz in Servern und leistungsfähigen Desktop-Computern, die im Jahr 2000 mit 1,4 und 1,5 GHz Prozessortakt eingeführt wurde. Die Pentium 4-Prozessoren implementieren Intels NetBurst-Architektur. Deren „Philosophie“ ist es, durch eine lange, fein granulierte Pipeline hohe Taktraten zu ermöglichen. Eine schnelle Ausführung ist dann möglich, wenn die Prozessorsteuerung und das Speichersystems die Pipeline schnell genug mit Instruktionen und Operanden beschicken kann. Dies hängt dann vom auszuführenden Befehlsstrom ab.

Neben der Steigerung der Taktrate und mehreren Ausführungen mit verschiedener Cache-Konfiguration, wurde auch der Prozessorkern überarbeitet und dabei Befehlssatz und Fähigkeiten erweitert. Die Beschreibung bezieht sich deshalb auf die im Testrechner vorhandene Version, der die dritte Überarbeitung des Prozessor-Kerns mit dem Namen Prescott enthält.

#### 4.1.1 Befehls- und Registersatz

Der Intel Pentium 4 führt den IA-32-Befehlssatz (Intel 80386-Prozessor) mit einigen Erweiterungen aus. Hierfür stehen acht 32 Bit-Register zur Verfügung, die teilweise als Allzweck-Register genutzt werden können, bei einigen Instruktionen allerdings auch spezielle Bedeutung erhalten. Des Weiteren existieren acht stapel-ähnlich organisierte 80 Bit breite Fließkommaregister.

Erweiterungen waren insbesondere die schrittweise eingeführten SIMD-Instruktionen: Die im Pentium MMX eingeführten Befehle mit Verwendungsschwerpunkt Multimedia ermöglichen Berechnungen mit Vektoren aus Integerzahlen auf acht 64 Bit breiten Vektorregistern, die intern allerdings gemeinsam mit den x87-FPU-Registern realisiert und deshalb nicht unabhängig sind (*Multi Media Extension*). Im Pentium III wurde dann die SSE (*Streaming SIMD Extension*) eingeführt, die zunächst nur die Verarbeitung von Vektoren aus maximal vier Fließkommawerten einfacher Genauigkeit auf acht neuen 128 Bit breiten Vektorregistern, auch mit Operanden aus dem Speicher, ermöglichte und neue MMX-Befehle hinzufügte (zum Teil als *MMX2* bezeichnet). Die mit den ersten Pentium 4 eingeführte SSE2 erweiterte den Vektor-Befehlssatz auf die 128-bittigen Vektorregister deutlich und ermöglichte dann die Verarbeitung von einzelnen Werten oder kompletten 16 Byte-Vektoren aller üblichen Datentypen, also 1, 2, 4 und 8 Byte großen Ganzzahlen und Fließkommazahlen einfacher und doppelter Genauigkeit. Die SSE3 des Prescott-Kerns brachte einige spezielle SIMD-Befehle, insbesondere horizontal auf den Vektoren arbeitende Operationen mit Einsatzschwerpunkt Video-Bearbeitung.

#### 4.1.2 Prozessorkern

Die CISC-Befehle des IA-32-Befehlssatzes eignen sich wegen ihrer verschiedenen Länge und ihrer stark unterschiedlichen Komplexität nicht direkt zu Pipelining. Befehle werden deshalb direkt nach dem Laden von einem Decoder in eine Folge mehrerer einfacher, RISC-ähnlicher und direkt ausführbarer Instruktionen übersetzt ( $\mu$ ops) und unter Beibehaltung der Reihenfolge in einem speziellen Instruktionscache (dem sogenannten *Execution Trace Cache*) gespeichert.

Eine Einheit aus fünf Schedulern wählt hieraus ausführbereite und nicht durch Abhängigkeiten blockierte  $\mu$ ops aus und übergibt diese an die superskalar ausgelegten Recheneinheiten. Die Retirement-Einheit ordnet die Ergebnisse der  $\mu$ ops (*Commitment*) und sorgt dafür, dass die IA-32-Instruktionen in ihrer ursprünglichen Reihenfolge abgeschlossen (*Retirement*) und mögliche Ausnahmen angezeigt werden. Die *Rapid Execution Engine* (Rechenkern abzüglich der Dekodiereinheit) ist als 31-stufige Pipeline ausgelegt (ältere Pentium 4: 20 Stufen).

Der Decoder kann pro Takt eine IA-32-Instruktion, der maximal 3  $\mu$ ops entsprechen, übersetzen und im Execution Trace Cache ablegen. Komplexere IA-32-Instruktionen müssen allerdings mit Hilfe eines speziellen ROMs in *Microcode*-Folgen übersetzt werden, deren Dekodierung und Ausführung ineffizienter ist.

Die Schedulereinheit aus fünf Einzelschedulern kann maximal 6 $\mu$ ops pro Takt in Auftrag geben, was allerdings die Leistungsfähigkeit des Trace Cache übersteigt. Zur Verfügung stehen folgende Einheiten:

- eine doppelt getaktete Integer ALU für Addition/Subtraktion

- eine weitere doppelt getaktete Integer ALU, die zusätzlich für Logik, Sprünge und Speichern genutzt werden kann

- eine ALU für Integer-Multiplikationen

- eine Fließkommaeinheit zum Bewegen, Speichern und Tauschen von Fließkommawerten

- eine Cluster-artig ausgelegte FPU mit sieben Untereinheiten, die unter anderem auch für SIMD inklusive Integer zuständig sind

- eine Adress-Einheit (*Address Generation Unit*) zum Laden und Prefetchen

- ein weiteres AGU zum Speichern.

Eine der beiden doppelt getakteten Fließkommaeinheiten ist auch zu Schiebe- und Rotieroperatoren fähig.

Zu Taktbeginn können die Scheduler durch insgesamt vier Ports vier Operationen starten und zur Takthälfte nochmals durch zwei Ports die doppelt getakteten ALUs beschicken. Allerdings können einige Untereinheiten nach Beginn einer Ausführung erst mit wenigen Takten Verzögerung eine neue Instruktion annehmen.

Pro Takt können eine Lese- und eine Schreiboperation auf den Speicher gestartet werden, auch Out of Order und, soweit keine TLB-Misses auftreten, bei spekulativer Ausführung. Acht ausstehende Leseoperationen können verwaltet werden. Für Schreiboperationen werden insgesamt 48 *Store Buffer* genutzt, wodurch Befehle bereits vor Ausschreiben in die Speicherhierarchie intern abgeschlossen werden können. Auf 36 ausstehende Schreiboperationen kann gleichzeitig gewartet werden. Werden Operanden aus dem Hauptspeicher benötigt, die wegen einer vorhergehenden Schreiboperation noch in einem Store Buffer verweilen, können diese ohne Umweg über die Caches als Operanden verwendet werden (*Store Forwarding*).

Der Scheduler geht grundsätzlich davon aus, dass benötigte Daten im Level 1 Cache vorhanden sind. Ist dies nicht der Fall, arbeiten die  $\mu$ ops zunächst mit falschen Operanden und müssen später mit den korrekten Operanden wiederholt werden (*Replay*).

### 4.1.3 Speicherhierarchie

Der Pentium 4 der fauia42 realisiert eine zweistufige Speicherhierarchie mit getrennten Level 1-Caches und einem gemeinsame Level 2-Cache. Der Level 1-Cache besteht aus dem in Absatz 4.1.2 erwähnten Execution Trace Cache für Instruktionen und einem Level 1 Data Cache. Die Caches sind nicht inklusiv. Schreiboperationen, deren Ziel noch nicht im Level 1-Cache vorhanden ist, werden ausschließlich in den Level 2-Cache geschrieben, im anderen Fall in beiden Cache-Levels aktualisiert (Write-Through). Die Daten-Caches realisieren eine Pseudo-Least-Recently-Used Verdrängungstrategie. Eine Aufstellung weiterer Eigenschaften ist in Tabelle 4.1 zu finden.

Tabelle 4.1: Überblick über die Caches der fauia42

|                      | L1 Trace Cache                    | L1 Data Cache                                 | L2 Cache                    |

|----------------------|-----------------------------------|-----------------------------------------------|-----------------------------|

| Größe                | 12 k $\mu$ ops                    | 16 kB                                         | 1 MB                        |

| Cachezeile           | keine Angabe                      | 64 Byte                                       | 64 Byte (effektiv 128 Byte) |

| Assoziativität       | achtfach                          | achtfach                                      | achtfach                    |

| Anbindung            | keine Angabe                      | 64 Bit (128 Bit zum Laden der Vektorregister) | 256 Bit                     |

| Operationen pro Takt | je 3 $\mu$ op Lesen und Schreiben | ein Load und ein Store                        | ein Load oder ein Store     |

| Latenz               | keine Angabe                      | nach Größe 4 bis 12 Zyklen                    | 7 Zyklen                    |

Zudem verfügt der Pentium 4 Prescott über acht *Write Combining Buffers*. Diese werden auch genutzt, wenn Store Misses im Level 1-Cache auftreten, um den Transfer zum Level 2-Cache zu erhöhen.

Der Pentium 4 besitzt außerdem getrennte Translation Lookaside Buffer für Instruktionen und Daten. Diese besitzen jeweils 64 Einträge für 4 kB große Seiten und sind voll assoziativ. Größere Seiten müssen fragmentiert gespeichert werden.

### 4.1.4 Prefetcher

Der Prescott-Kern verfügt über Hardware-Prefetcher für Instruktionen und Daten. Der Instruktionsprefetcher lädt die nächsten 64 Byte des IA-32-Bytecode in 32 Byte-Blöcken, auch in Kooperation mit der Branch Prediction. Der Daten-Prefetcher kann bis zu acht kontinuierliche Lese- oder Schreibströme erkennen, allerdings maximal einen pro 4 kB-Speicherblock. Er lädt 128 Byteweise, allerdings maximal bis zum Ende eines 4 kB-Blocks. Er versucht dabei, 256 Byte vor dem tatsächlichen Datenstrom zu bleiben. Beide Prefetcher laden Cache-Zeilen in den Level 2-Cache.

Der erweiterte Instruktionssatz enthält außerdem spezielle Prefetch-Instruktionen, die dem Prefetcher allerdings nur als Hinweis dienen, und die er – z. B. bei fehlender freier Bandbreite – ignorieren kann.

Ein implizites Prefetching findet außerdem immer statt, wenn Daten vom Hauptspeicher in den Level 2-Cache gelesen werden, da hier stets eine zweite benachbarte Zeile mit eingelagert wird.

## 4.2 AMD Athlon64 4000+ 2,4 GHz fauia49.informatik.uni-erlangen.de

AMDs Athlon Prozessoren können zum einen als Konkurrenzprodukt zu Intels Prozessorserie gesehen werden, die denselben Bytecode akzeptieren. Intern haben sie allerdings ein vollständig eigenes Design und bietet zusätzliche Fähigkeiten und einen noch größeren Befehlssatz.

### 4.2.1 Befehls- und Registersatz

Der AMD Athlon64 4000+ der Fauia49 akzeptiert zunächst den IA-32 Bytecode des Intel Pentium 4 (mit Ausnahme der neuen SSE3-Instruktionen) und bietet zunächst denselben Registersatz. Die von Intel mit MMX, SSE und SSE2 eingeführten Instruktionen sind dort Teil der 3Dnow! und 3Dnow! Professional Erweiterungen. Allerdings wurden dabei auch weitere Instruktionen hinzugefügt. Der Athlon 4000+ der Fauia49 enthält den „Hammer“ Prozessorkern. Mittlerweile sind auch neuere Kerne, unter derselben Prozessorbezeichnung, verfügbar, die auch SSE3-Instruktionen ausführen können.

Der Athlon64 ist grundsätzlich als 64 Bit-Prozessor konzipiert, der bei entsprechender Betriebssystemunterstützung einen größeren Adressraum und einen erweiterten Registersatz bietet. Im 64 Bit-Modus können die acht Allzweckregister auch 64 Bit breit genutzt werden, außerdem stehen acht weitere 64-bittige Allzweckregister und acht zusätzliche 128 Bit-Vektorregister für SIMD-Operationen zur Verfügung.

### 4.2.2 Prozessorkern

Um die komplexen Operationen des Befehlssatzes effizient verarbeiten zu können, werden diese auch vom Athlon64 in kleinere, RISC-ähnliche Instruktionen zerlegt. AMD hat sich hier allerdings für ein mehrstufiges Konzept entschieden.

Die Instruktionen werden nach dem Laden mit Zusatzinformationen, die effizientere Dekodierung und Ausführung ermöglichen, im Level 1-Instruktions-Cache abgelegt. Von einer Hol- und Dekodiereinheit wird der daraus gelesene Instruktionsstrom in ursprünglicher Reihenfolge in *macro-ops* umgewandelt und einer zentralen Kontrolleinheit (*Instruction Control Unit*) übergeben, wo sie in einem Puffer zwischengespeichert werden. Aus diesem Puffer kann das ICU macro-ops an die Integer- oder Fließkomma-Scheduler unter Beachtung von Abhängigkeiten und vorhandenen Ressourcen zur Ausführung übergeben. Das ICU ist auch für das Retirement der macro-ops, Ausnahmen, Unterbrechungen und die Behandlung falscher Sprungvorhersagen zuständig, sowie das Register Renaming der Integer-Einheiten.

Die Dekodiereinheit besteht aus drei Einzeldekodern und kann pro Takt maximal 3 macro-ops erzeugen. Einfache IA-32 bzw. AMD64-Instruktionen können direkt in ein oder zwei macro-ops übersetzt werden (*direct path, double*), komplexe Instruktionen müssen in einem ROM nachgeschlagen werden (*vector path*) und können das gleichzeitige Dekodieren von Direct Path-Instruktionen verhindern.

Die drei Integer-Scheduler, denen jeweils eine ALU und ein Adressiereinheit angeschlossen sind, zer teilen die macro-ops in kleinere *micro-ops*, die wiederum bei verfügbaren Operanden Out of Order direkt von der Hardware ausgeführt werden können. Alle drei ALU/AGU-Einheiten beherrschen alle logischen und arithmetischen Operationen und Adressierfunktionen mit Ausnahme der Multiplikation; hierfür steht eine spezielle Einheit zur Verfügung, zu deren Nutzung zwei ALUs synchron genutzt werden müssen.

Die Fließkommaeinheit ist als eigenständiger mathematischer Koprozessor ausgelegt, der ein eigenes Register File verwaltet. Aufgabe der FPU ist die Ausführung aller x87, MMX, SSE und SSE2-Instruktionen und der AMD-eigenen 3Dnow! Erweiterungen. Dies schließt auch einige Integer-Operationen mit ein. Der Fließkomma-Scheduler übersetzt die macro-ops in micro-ops und kann maximal drei micro-ops pro Takt an folgende Einheiten übergeben:

- eine Einheit für einfache logische und arithmetische Operationen

- eine Einheit für komplexere Operationen wie Multiplikation, aber auch Division und Wurzel

- eine Einheit, die zum Schreiben und für einige komplexe Vector Path-Instruktionen genutzt wird

Die Fließkommaeinheit unterstützt außerdem ein spezielles Chaining: Werden Operanden durch eine reine Ladeoperation vom Speicher in ein Register geholt und anschließend durch die FPU

verarbeitet, können diese Daten bereits vor Abschluss der Lade-Instruktion genutzt werden (*Super Forwarding*).

Speicherzugriffe werden zentral durch das *Load-Store Unit* verwaltet. Dieses kann zwölf Zugriffe auf den Level 1-Cache verwalten. Bei Cache Misses werden diese Operationen in einer weiteren Warteschlange mit 32 Einträgen über den Level 2-Cache abgehandelt oder initiieren Hauptspeicherzugriffe. Das LSU ist auch für die Einhaltung der semantischen Ausführungsreihenfolge verantwortlich. Die LSU kann maximal zwei Operationen über jeweils maximal 64 Bit pro Taktzyklus durchführen und beschränkt damit den Datendurchsatz des Prozessors auf maximal 16 Byte pro Takt.

#### 4.2.3 Speicherhierarchie

Die Cachehierarchie ist zweistufig mit getrennten Instruktions- und Datencaches auf Level 1 und einem gemeinsamen Level 2-Cache. Im Level 1-Instruktions-Cache wird ein kommentierter Bytecode, der neben Hinweisen für eine schnellere Dekodierung auch Daten über das bisherige Verhalten bei bedingten Sprüngen für die Branch Prediction enthält, abgelegt. Somit bleiben diese Informationen auch bei Verdrängung in den Level 2-Cache erhalten.

Instruktionen und Daten werden primär nur in den Level 1-Cache geladen. Der Level 2-Cache ist exklusiv und enthält nur Daten, die entweder aus dem Level 1-Cache verdrängt oder verändert wurden und später in den Hauptspeicher geschrieben werden müssen (*Victim or Copy-Back*).

Im Gegensatz zu den meisten anderen Prozessoren benötigt der Athlon64 keine Northbridge auf der Hauptplatine. Stattdessen besitzt er einen integrierten Memory Controller, der dadurch die Latenz zum DDR-SDRAM verkürzt. Zur Kommunikation mit Peripherie-Geräten wird die HyperTransport-Technologie eingesetzt. Weitere Informationen über die Caches sind Tabelle 4.2 zu entnehmen.

Tabelle 4.2: Überblick über die Caches der fauia49

|                | <b>L1 Instr. Cache</b> | <b>L1 Data Cache</b> | <b>L2 Cache</b> |

|----------------|------------------------|----------------------|-----------------|

| Größe          | 64 kB                  | 64 kB                | 1 MB            |

| Cachezeile     | 64 Byte                | 64 Byte              | 64 Byte         |

| Assoziativität | zweifach               | zweifach             | 16-fach         |

Der Athlon64 organisiert auch die Translation Lookaside Buffer hierarchisch. Die getrennten Level 1 Instruction und Data TLBs sind voll assoziativ und können 16 4 kB- sowie acht 2 MB- oder vier 4 MB-Seiten verwalten. Der exklusive Level 2 TLB umfasst 256 4 kB-Seiten.

Athlon64 Prozessoren besitzen mindestens vier Write Combining Buffer. Diese werden allerdings nur für spezielle Speicherbefehle genutzt (siehe 5.3).

#### 4.2.4 Prefetcher

Der AMD Athlon64 bietet ein implizites Instruktions-Prefetching, indem bei einem Cache Miss stets die folgende Cache-Zeile mit eingelagert wird.

Der Hardware-Prefetcher orientiert sich an Zugriffen auf aneinander liegende Cachelines: Werden Cachezeile  $n$  und Cachezeile  $n + 1$  nacheinander adressiert, lädt er Cachezeile  $n + 3$  in den Speicher. Über die Anzahl erkennbarer Datenströme, oder ob dieser Prefetcher auch den Instruktions-Strom berücksichtigt, ist der Dokumentation nichts zu entnehmen. Maximal auf acht Prefetches kann gewartet werden, die allerdings nur bei freien Ressourcen durchgeführt werden.

Der Athlon64 unterstützt zum einen die Prefetch-Instruktionen des erweiterten IA-32-Befehlssatzes und lädt damit Daten in den Level 1 Data Cache. AMDs 3Dnow! bietet außerdem zwei weitere Prefetch-Befehle, die ebenfalls Daten in den Level 1 Cache laden. Hierunter ist auch ein spezielle Anweisung zum Prefetchen von Daten, die geändert werden sollen.

# Kapitel 5

## Angewandte Optimierungsverfahren

### 5.1 Datenlayout

Ein großes Potential liegt in den Vektoreinheiten der Testsysteme. Ein Datenlayout sollte deshalb deren Verwendung nicht nur als schnelle skalare FPU, sondern auch eine effiziente Verarbeitung von ganzen Vektoren von Werten ermöglichen. In den folgenden Kapiteln sollen deshalb Voraussetzungen für solch ein Layout sowie deren genaue Realisierung in zwei und drei Dimensionen erklärt werden.

Grundsätzlich profitieren Prozessoren von einer angepassten Ausrichtung von Daten im Speicher. Da moderne Caches nicht Byte-genau adressiert werden können, müssen ungünstig liegende Operanden möglicherweise in zwei Teilen getrennt übertragen werden. Werden Daten *natürlich* im Speicher ausgerichtet, das entspricht bei den üblichen  $2^n$  Byte großen Datentypen einer Ausrichtung an einem Vielfachen ihrer Größe, kann dies ausgeschlossen und eine schnelle Verarbeitung sichergestellt werden.

Da der Zugriff auf nicht ausgerichtete Daten auch eine entsprechend aufwendige Unterstützung durch die Hardware voraussetzt, bieten die SIMD-Einheiten beider Prozessoren nur spezielle, langsamere Lade- und Schreiboperationen, mit denen Vektoren vollständig oder in Teilen übertragen werden können. Als Operanden für Vektorberechnungen können nur natürlich ausgerichtete Vektoren oder Registerinhalte genutzt werden.

Das vorgeschlagene Datenlayout geht bei der Unterstützung der vektorisierten Berechnung von 128 Bit großen Vektoren aus zwei Fließkommazahlen doppelter Genauigkeit aus. Der Ansatz lässt sich aber auch für andere Vektorgrößen und Datentypen verallgemeinern.

#### 5.1.1 Anpassung des Datenlayouts für 2D

Ziel ist es, statt der aufeinander folgenden getrennten Berechnungen

$$U_{x,y} = \frac{1}{4}(U_{x-1,y} + U_{x+1,y} + U_{x,y-1} + U_{x,y+1} - (dh^2 \cdot F_{x,y}))$$

und

$$U_{x+2,y} = \frac{1}{4}(U_{x+1,y} + U_{x+3,y} + U_{x+2,y-1} + U_{x+2,y+1} - (dh^2 \cdot F_{x+2,y}))$$

die Vektorrechnung

$$\begin{bmatrix} U_{x,y} \\ U_{x+2,y} \end{bmatrix} = \frac{1}{4} \left( \begin{bmatrix} U_{x-1,y} \\ U_{x+1,y} \end{bmatrix} + \begin{bmatrix} U_{x+1,y} \\ U_{x+3,y} \end{bmatrix} + \begin{bmatrix} U_{x,y-1} \\ U_{x+2,y-1} \end{bmatrix} + \begin{bmatrix} U_{x,y+1} \\ U_{x+2,y+1} \end{bmatrix} - dh^2 \cdot \begin{bmatrix} F_{x,y} \\ F_{x+2,y} \end{bmatrix} \right)$$

auszuführen. Für den dreidimensionalen Fall gilt dies analog. Dieser wird in Abschnitt 5.1.2 genauer behandelt.

Die Anforderungen an das Speicherlayout sind folgende:

1. die Paare eines Vektors sollen direkt nebeneinander im Speicher liegen

2. möglichst viele für eine Berechnung verwendete Vektoren sollen natürlich, also an 16 Byte-Grenzen, ausgerichtet sein

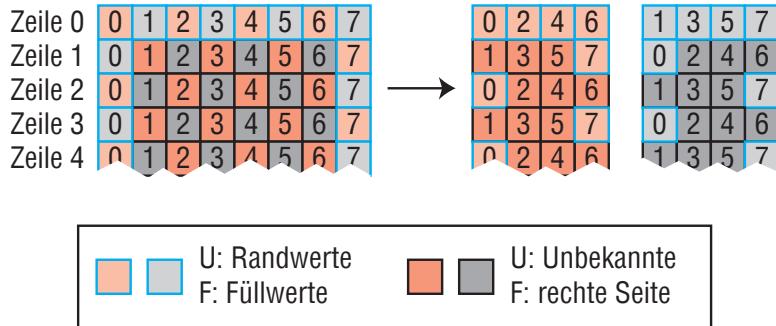

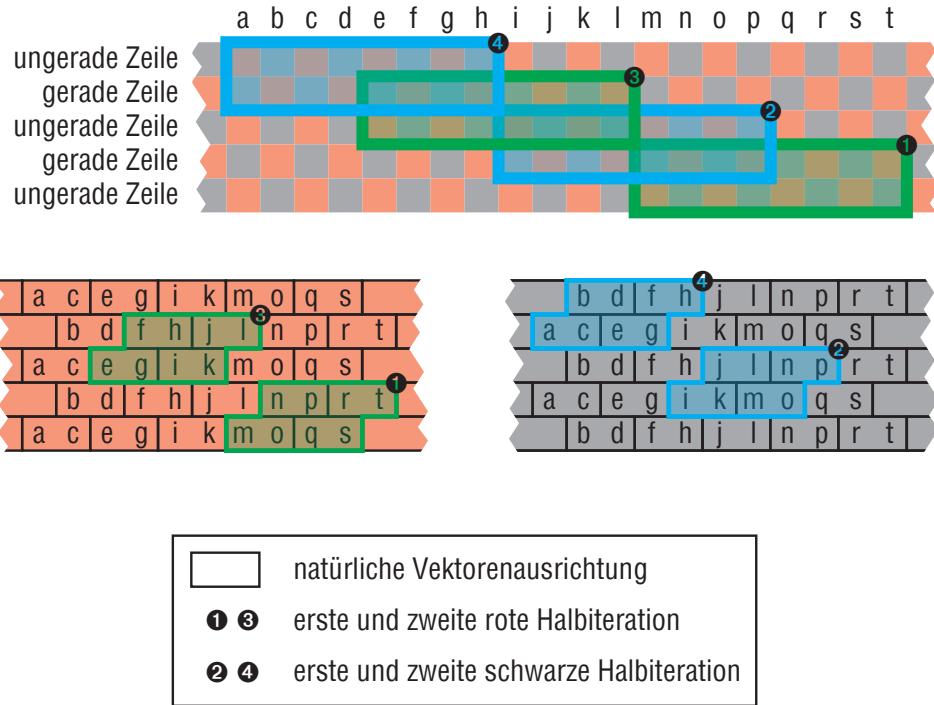

Anforderung 1 lässt sich durch zeilenweises Auftrennen der beiden Felder  $U$  mit den Unbekannten und Randwerten und  $F$  mit der rechten Seite der Gleichungen in jeweils zwei neue Arrays bewerkstelligen, die entweder nur rote oder schwarze Werte enthalten. Die Bezeichnungen „rot“ und „schwarz“ werden hier auch auf die Werte aus  $F$  und die Randwerte in  $U$  verallgemeinert (vgl. Abbildung 5.1).

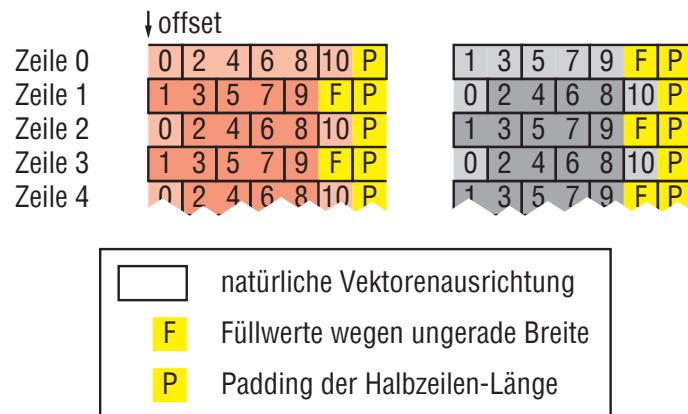

Bei einem  $x \times y$  großen Problem werden mit Randwerten sonst  $(x+2) \times (y+2)$  große Felder benötigt. Durch die Auftrennung entstehen zwei neue Felder mit  $(y+2)$  Halbzeilen. Ist  $x$  gerade, so enthält jede Zeile gleich viele rote und schwarze Werte, und jede Halbzeile enthält  $x/2$  Unbekannte und einen Randwert zu Beginn oder am Ende. Ist  $x$  allerdings ungerade, so enthalten die Zeilen unterschiedlich viele rote und schwarze Werte, und dementsprechend sind die *geraden* Halbzeilen mit  $y=0, 2, \dots$  und die *ungeraden* Halbzeilen unterschiedlich lang. Mit Ausnahme der Halbzeilen 0 und  $y+1$ , die ausschließlich Randwerte enthalten, enthält eine Halbzeile dann entweder nur  $(x+1)/2$  Unbekannte oder  $(x-1)/2$  Unbekannte und zwei Randwerte. In der Praxis sollte hier allerdings eine gleiche Zeilenbreite gewählt werden und in den kürzeren Zeilen Speicher ungenutzt bleiben, um das Feld auch in Hochsprache als Array ansprechen zu können.

Abbildung 5.1: Trennung der roten und schwarzen Werte in 2D

Speicherausrichtung lässt sich für alle Paare mit Ausnahme der Vektoren  $(U_{x-1,y}; U_{x+1,y})$  und  $(U_{x+1,y}; U_{x+3,y})$  erreichen, die offensichtlich nicht beide gleichzeitig im Speicher entsprechend ausgerichtet sein können. Um Berechnungen möglichst über die ganze Zeile vollständig mit Vektoroperationen durchführen zu können, werden die ersten Unbekannten jeder Zeile an 16 Byte-Grenzen ausgerichtet.

Für den beschriebenen Fall mit Vektoren aus zwei Fließkommazahlen kann man dies sehr leicht erreichen, indem man zunächst mit Padding die Länge einer Halbzeile auf eine ungerade Anzahl von Werten bringt, wenn dies nötig ist. Dann wird der Beginn der schwarzen Felder an 16 Byte-Grenzen und der roten Felder an 16 Byte-Grenzen mit einem Offset von 8 Byte ausgerichtet.

Ist die Anzahl an Unbekannten in einer Zeile  $x$  ganzzahlig durch vier teilbar, so können alle Berechnungen vektorisiert durchgeführt werden. Andernfalls kann am Ende einer Zeile noch eine Berechnung mit nur einem Teilvektor notwendig sein, was in diesem Fall einer skalaren Berechnung entspricht. Abbildung 5.2 zeigt hierfür ein Beispiel.

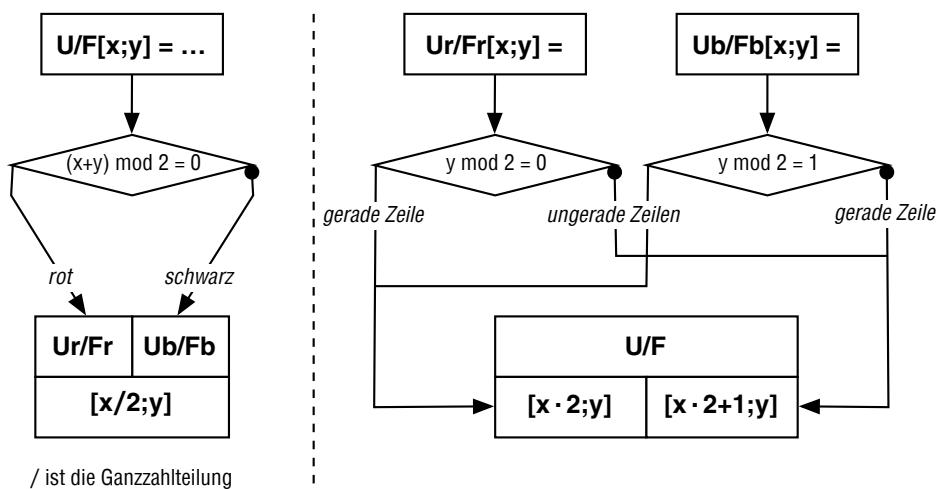

Die Punkte können getrennt dann nicht mehr mit den bisherigen Indizes adressiert werden. Abbildung 5.3 zeigt die Zuordnung zwischen den gemeinsamen und den getrennten Feldern. In der Praxis ist eine transparente Zuordnung zwischen der getrennten Speicherung und dem zu Grunde liegenden Gitter – z.B. über Unterfunktionen – innerhalb des Lösers nicht sinnvoll.

Abbildung 5.2: Layout der roten und schwarzen 2D-Arrays bei  $x = 9$

Abbildung 5.3: Zuordnung zwischen getrennten und gemeinsamen Feldern

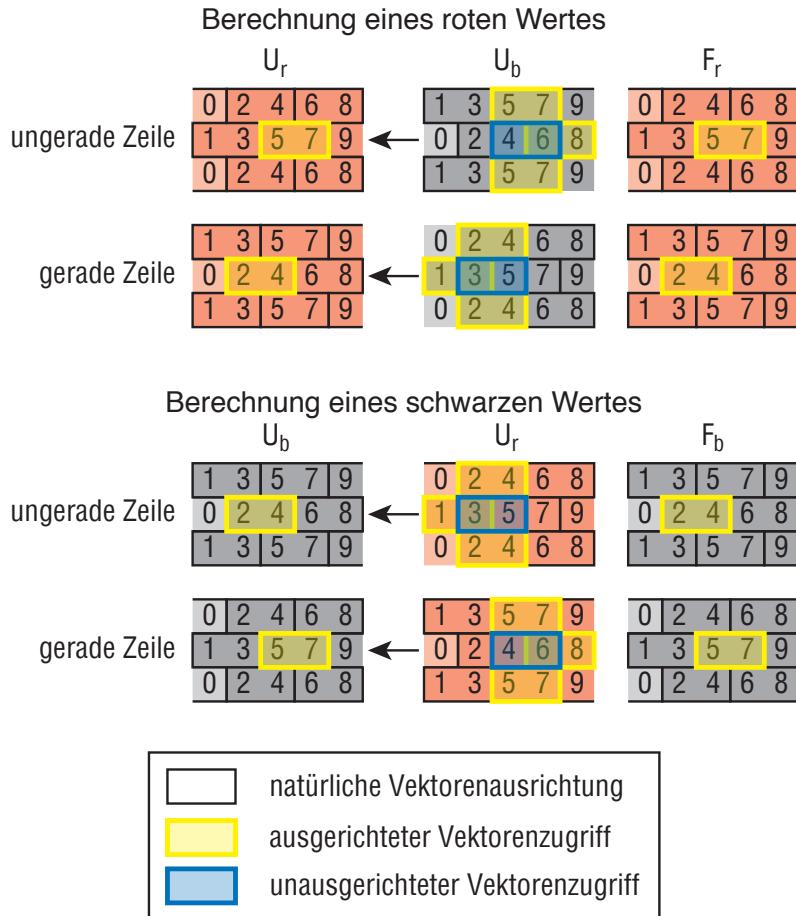

Für die Implementierung ist die Sicht auf gemeinsame Felder auch nicht nötig. Eine Iteration bedeutet hier nur, zunächst alle Unbekannten in  $U_r$  und danach alle Unbekannten in  $U_b$  zu berechnen. Dazu müssen allerdings zwei leicht unterschiedliche Stempel genutzt werden (siehe Abbildung 5.4), die jeweils auch noch in zwei Varianten entweder Werte in  $U_r$  aus  $U_b$  oder umgekehrt berechnen. Von ihrer „Form“ und ihren ausgerichteten und unausgerichteten Zugriffen gleichen sich die Berechnungen von „roten ungerade“ und „schwarzen geraden“ Zeilen einerseits, und den anderen Zeilen andererseits. Bei getrennten Arrays lautet die Berechnung für Halbzeilen, die mit einem Randwert beginnen

$$U_{r/b}[x; y] = \frac{1}{4} (U_{b/r}[x, y - 1] + U_{b/r}[x, y + 1] + U_{b/r}[x; y] + U_{b/r}[x + 1; y] - dh^2 \cdot F_{r/b}[x; y])$$

und für die anderen

$$U_{r/b}[x; y] = \frac{1}{4} (U_{b/r}[x, y - 1] + U_{b/r}[x, y + 1] + U_{b/r}[x - 1; y] + U_{b/r}[x; y] - dh^2 \cdot F_{r/b}[x; y])$$

Bei vektorsierten Berechnungen ist jeweils der Vektor  $(U_{b/r}[x; y]/U_{b/r}[x + 2; y])$  nicht natürlich im Speicher ausgerichtet.

Abbildung 5.4: Diskreter Fünf-Vektor-Stempel in 2D

Für beliebig große Vektoren aus beliebigen Datentypen ist dieser Ansatz jedoch nicht ohne weiteres übertragbar. Eine Möglichkeit wäre es hier, die effektive Zeilenlänge auf ein Vielfaches der Vektorgröße zu padden und jede Zeile mit einer Unbekannten beginnen zu lassen. Randwerte an der linken Seite werden dann an das Ende der vorhergehenden Halbzeile geschoben. In einigen Programmiersprachen ist der Arrayzugriff mit negativen Indizes durchaus möglich. In C z. B., wo man die Indizes wegen der *column first*-Schreibweise bei Arrays umdrehen sollte, ist ein Zugriff auf  $Ur[3][-1]$  möglich.

Die Auftrennung der Werte in Halbfelder führt auch zu einer effizienteren Cache-Nutzung: Bei einer Berechnung mit gemischten Feldern liegen schwarze und rote Werte innerhalb einer Zeile alternierend im Speicher. So werden bei jeder Halbiteration auch unbenötigte Werte aus  $F$  in den Speicher geladen. Aber auch für die Werte aus  $U$  bringt dies Vorteile, wenn nicht alle Werte der vorher berechneten Zeile im höchsten Cachelevel verweilen können. Für die Berechnung der Zeile  $y$  werden bei gemischten Feldern die vollständigen Zeilen  $y - 1$  und  $y + 1$  in den Level 1 Cache geladen, obwohl nur eine Farbe davon benötigt würde.

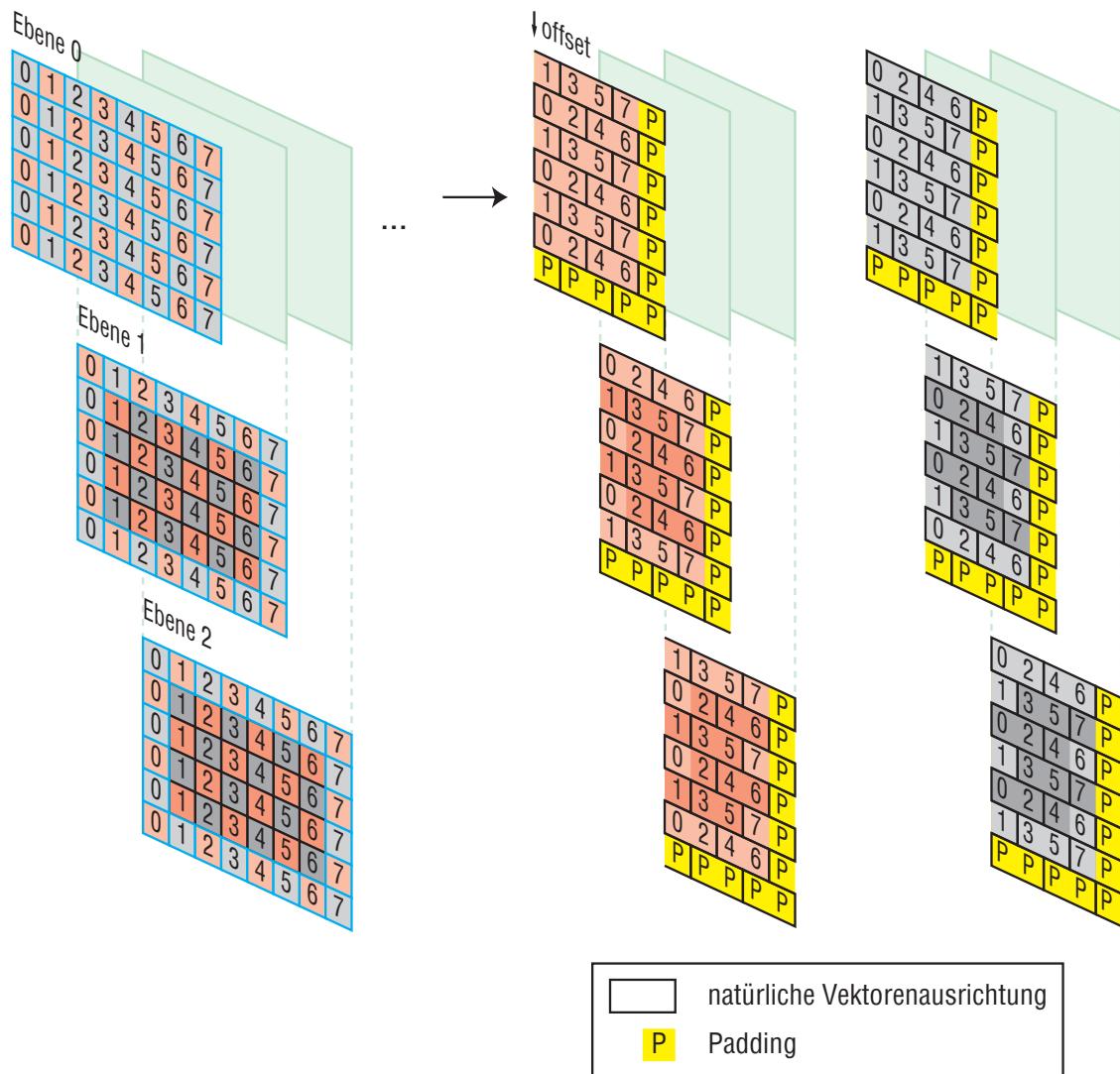

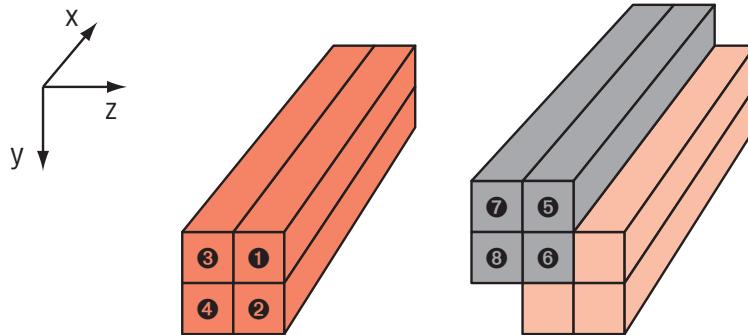

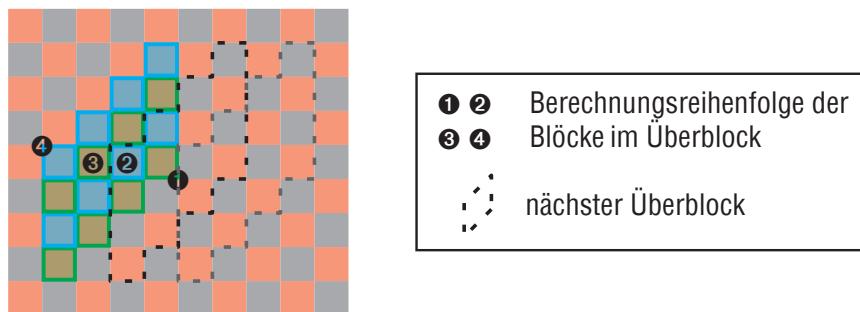

### 5.1.2 Erweiterung auf 3D

Dieses Speicherlayout mit getrennten Feldern kann auch auf den dreidimensionalen Fall erweitert werden. Hier lässt sich das dreidimensionale Gitter als Aneinanderreihung mehrerer zweidimensionaler Ebenen betrachten, innerhalb derer sich das Speicherlayout wie in Abschnitt 5.1.1 beschrieben anpassen lässt. *Ungerade* Ebenen mit  $z = 1, 3, \dots$  entsprechen hier dem zweidimensionalen Fall, in den *geraden* Ebenen mit  $z = 0, 2, 4, \dots$  ist die Verteilung von roten und schwarzen Punkten genau invertiert. Um die Bezeichnung gerader und ungerader Zeilen konsistent zu halten, werden im folgenden die Zeilen mit  $y + z \bmod 2 = 0$  als ungerade Zeilen bezeichnet, da der Randwert am Anfang dieser Zeilen wie in 2D den schwarzen Halbfelder zugeordnet wird.

Da die erste Ebene mit einem schwarzen (aber nie benötigten) Randwert  $U[0; 0; 0]$  beginnt, müssen in diesem Fall die Ausrichtungen der Arrays gegenüber der 2D-Variante vertauscht werden, also  $U_r$  und  $F_r$  werden direkt an 16-Byte-Grenzen ausgerichtet, und  $U_b$  und  $F_b$  mit einem Offset von acht Byte.

Des weiteren muss sichergestellt werden, dass auch in den folgenden Ebenen eine entsprechende Speicherausrichtung besteht. Enthält eine Ebene eine ungerade Anzahl von Halbzeilen, so belegt eine Halbebene wegen der Halbzeilen ungerader Länge auch ein ungerades Vielfaches von 8 Byte, und die folgenden Halbebenen sind jeweils entsprechend ausgerichtet. Im anderen Fall ist ein Padding mit acht Byte am Ende jeder Halbebene theoretisch ausreichend, aber durch das Anhängen einer leeren Halbzeile an jede Ebene bleibt sinnvoller Zugriff auf Hochsprachenebene möglich.

Bei der Berechnung im Dreidimensionalen entsprechen die Zugriffe innerhalb der Ebene auf  $U[x \pm 1; y; z]$  und  $U[x; y \pm 1; z]$  dem zweidimensionalen Fall. Die Halbzeilen, die die vorderen und hinteren Nachbarn  $U[x; y; z \pm 1]$  enthalten, sind ebenso wie die Zeilen mit  $U[x; y \pm 1; z]$  ausgerichtet. Damit ist auch auf diese Werte natürlich ausgerichteter Zugriff möglich.

Abbildung 5.5: Speicherlayout in 3D

## 5.2 Code-Optimierung

Eine große Rolle für die Ausführung des Codes spielt auch die Auswahl und Reihenfolge der Maschinensprache-Operationen. Bei Hochsprache wird diese von einem Compiler erzeugt und kann vom Programmierer oft nur mittelbar oder indirekt beeinflusst werden. Zu den Möglichkeiten des Programmiers zählen hier eine geschickte Auswahl von Hochsprache-Konstrukten und in einigen Fällen spezielle Hinweise an den Compiler, für C sind dies meist `#pragma`-Anweisungen oder Compiler-Flags.

Für große Software-Projekte ist die Programmierung in Assembler aus guten Gründen unüblich: Der Hochsprache-Code ist deutlich einfacher zu lesen und zu warten, während moderne Compiler sehr schnell mit vielen Optimierungen automatisch effiziente Befehlsfolgen erzeugen. Die Generierung von ähnlich „gutem“ Assembler-Code von Hand benötigt meist mehr Zeit und die Fehlerfreiheit ist ungleich schwerer zu sichern. Deshalb lohnt sich Assembler-Programmierung nur für relativ kleine und rechenintensive Programmteile, wie z. B. den Red-Black Gauss-Seidel.

### 5.2.1 Ablaufkontrolle und Adressierung

Zur Ausführungssteuerung werden alle acht Allzweckregister vorgesehen. Da keinerlei Unterfunktionsaufrufe stattfinden, werden vorübergehend alle Registerwerte auf dem Stapel abgelegt, und auch der Stack Pointer im Speicher ausgelagert. Dadurch ist es möglich, alle Schleifenvariablen und Zeiger im Prozessor zu halten. Die für Schleifen und Adressberechnung benötigten Operanden werden als direkte Operanden der Befehle im Instruktionsstrom eingelagert, so dass der Level 1 Data Cache ausschließlich für die eigentliche Berechnung zur Verfügung steht.

Die augenblickliche Position in den Feldern wird über einen einzigen Zeiger verwaltet, die Operanden im Speicher werden dann durch einen konstanten Wert und dem Zeiger als Offset adressiert. Dynamischer Speicher kann nur eingeschränkt genutzt werden, da hierfür insgesamt vier Zeiger nötig wären, davon drei jeweils für Berechnungen in einer Farbe. Allerdings gibt es die Möglichkeit, einen einzigen großen Speicherblock zu allozieren, der intern in die vier Halbfelder aufgeteilt wird. Seine Anfangsadresse wird in einem reservierten Register abgelegt, und Speicherzugriffe müssen dann mit einem konstanten Wert und zwei Registern als Offset durchgeführt werden. Da die Feldgrößen zur Übersetzungszeit bereits festgelegt sind, können fast alle Änderungen des Zeigers mit einfachen Additionen durchgeführt werden.

### 5.2.2 Ausführung der Berechnungen

Alle Berechnungen werden auf der Vektoreinheit durchgeführt. Die konstanten Teile der Iterationsformel werden dauerhaft in zwei Vektorregistern abgelegt. Statt einer Division durch 4 bzw. 6 wird eine Multiplikation mit  $\frac{1}{4}$  bzw.  $\frac{1}{6}$  verwendet, da diese Operation äquivalent ist, aber vom Prozessor schneller ausgeführt werden kann. Statt  $\dots - dh^2 \cdot F[i; j]$  wird die äquivalente Berechnung  $\dots + (-dh^2) \cdot F[i; j]$  durchgeführt, in 3D analog. Dadurch werden nur Addition und Multiplikation benötigt. Diese konstanten Teil werden jeweils in der unteren und oberen Hälfte von Registern abgelegt, für die eigentlichen Berechnungen stehen danach noch sechs Vektorregister zur Verfügung.

Für eine vektorisierte Berechnung sind zwei Register notwendig. Der unausgerichtete Vektor aus  $U$  muss zunächst speziell geladen werden. In ein weiteres Register wird der Vektor aus  $F$  geladen und multipliziert. Alle weiteren Werte aus  $U$  sind ausgerichtet, so dass Additionen mit Operanden aus dem Speicher genutzt werden können. Nach Addition der beiden Register und der Multiplikation mit  $\frac{1}{4}$  bzw.  $\frac{1}{6}$  können diese Werte dann wieder ausgerichtet als Vektor in den Speicher geschrieben werden.

Vektorisierung entspricht implizit einem Loop Unrolling um den Faktor 2. Bei der Generierung des Assembler-Codes können allerdings längere Befehlssequenz aufgerollt werden. Dabei wird die entsprechende Verschiebung im konstanten Teil der Adressierung berücksichtigt, und das Register mit dem Zeiger muss währenddessen nicht geändert werden.

Für den Athlon64 und den Pentium 4 wird jeweils leicht unterschiedlicher Code generiert, dessen Scheduling jeweils an den Prozessor angepasst ist. Längere Code-Sequenzen werden für den Pentium 4 aus Templates für die skalare Berechnung eines Wertes und aus Mustern für die vektorisierte Berechnung von zwei, vier, sechs und zehn Werten zusammengesetzt. Für den Athlon64 stehen nur Codemuster für die einzelne skalare und die vektorisierte Berechnung von zwei Werten zur Verfügung, da durch das Überschneiden der Instruktionen mehrerer Berechnungen keine höhere Geschwindigkeit erreicht werden konnte.

Zudem werden zum Laden des unausgerichteten Vektors unterschiedliche Instruktionen genutzt. Beim Pentium 4 wird das untere Register mit der *movsd*-Anweisung geladen, so dass die höherwertige Registerhälfte gelöscht wird. Er kann Teile eines Registers nur durch eine logische Operation ändern, sodass ein Überschreiben effizienter ist. Der Athlon64 muss Vektoroperationen stets über zwei 64-bitige Zugriffe ausführen. Deshalb ist das ändern nur einer Registerhälfte mit *movlpd* schneller. Die zweite Registerhälfte muss auf beiden Prozessoren über die *movhpfd*-Instruktion dazugeladen werden.

### 5.3 Non-Temporal Moves

Caches basieren ursprünglich auf einem transparenten Konzept, das alle gelesen oder geschriebenen Daten gleich einlagert oder verdrängt. Dabei ist keine Unterscheidung möglich, ob Daten einmalig oder mehrfach benötigt werden. Dadurch können Daten, die nur einmalig gelesen oder geschrieben werden, häufig genutzte Daten aus den Caches verdrängen (*Cache Pollution*).

Um dem entgegenwirken zu können, wurden spezielle Schreib-Operationen eingeführt, sogenannte *Non-Temporal Moves*. Diese schreiben die Daten über spezielle Puffer an den normalen zeitabhängigen Cachebereichen vorbei, in denen dadurch mehr Raum für sinnvolle Zwischenspeicherung bleibt. Bei den Testsystemen wird dies über die Write Combining Buffer (vgl. Abschnitt 3.2.3) realisiert. Können die so gesammelten Daten einen kompletten RAM-Speicherblock füllen, kann dieser Bereich im Burst Mode überschrieben werden. Es ist in der Spezifikation nicht festgelegt, ab wann diese Daten tatsächlich in den Hauptspeicher ausgeschrieben werden, so dass dies auch erst in freien Bustakten durchgeführt werden kann.

Der erweiterte IA-32-Befehlssatz bietet für die SSE-Register entsprechende Schreibbefehle allerdings nur für vollständige 128 Bit-Vektoren. Bei getrennten Feldern dies für den Red-Black Gauss-Seidel mit getrennten Feldern mit Ausnahme nur skalar berechenbarer Werte am Rand gut nutzbar; für eine rote Halbiteration werden die neuen Werte mit Daten aus  $U_b$  und  $F_r$  berechnet und in  $U_r$  geschrieben und für die schwarze Halbiteration entsprechend entgegengesetzt.

Bei der Realisierung der Non-Temporal Writes in den Testsystemen treten allerdings Probleme auf, wenn wider Erwarten doch Daten aus der zu den so geschriebenen Daten gehörenden Cache-Zeile vorzeitig adressiert werden. Für Ein-Prozessor-Systeme droht hier einzig Geschwindigkeitsverlust, für Mehr-Prozessor-Systeme realisieren diese Non-Temporal Moves allerdings ein nur schwach geordnetes Konsistenzmodell. Demnach wird nur sichergestellt, dass auch tatsächlich die letzte Schreiboperation den endgültigen Wert einer Adresse festlegt, allerdings nicht, wann diese Änderungen für andere Prozessoren sichtbar wird. In diesem Fall kann über spezielle *fence*-Operationen sichergestellt werden, dass die Änderungen allgemein wirksam werden. Da durch die schwache Konsistenz kein exklusiver Zugriff nötig ist, können für die Reservierung eingesparte Buszyklen anderweitig genutzt werden, was zu einer höheren Transferrate an Nutzdaten führt.

Non-Temporal Loads sind nicht explizit verfügbar. Dieses Verhalten kann bedingt durch spezielle Prefetch-Instruktionen erreicht werden, wie in Abschnitt 5.5 genauer beschrieben wird.

### 5.4 Blocking

Unter Blocking versteht man Techniken, die Berechnungen zur besseren Nutzung der Caches in anderer Reihenfolge vornehmen, ohne den zu Grunde liegenden Algorithmus und das Ergebnis

zu ändern. Ist die Verarbeitungsgeschwindigkeit vor allem durch die Speicherbandbreite begrenzt, können solche Verfahren die größte Geschwindigkeitssteigerung bringen.

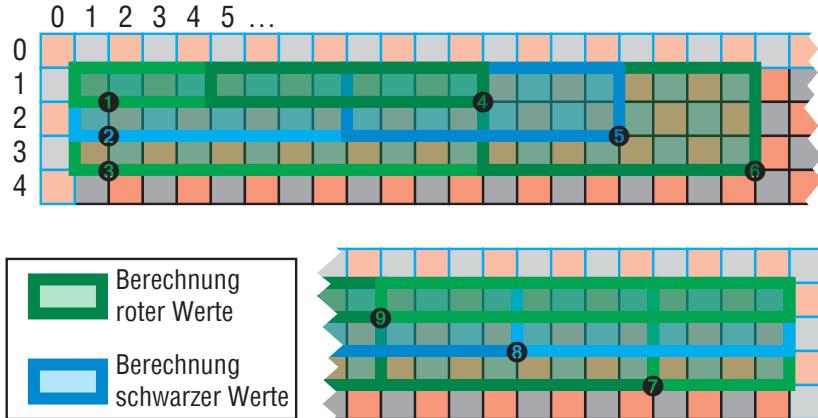

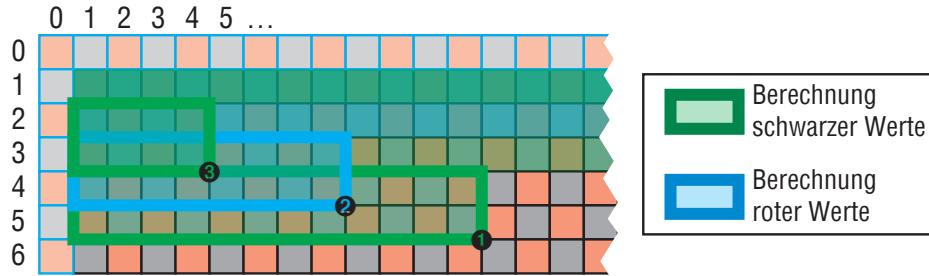

Für den Red-Black Gauss-Seidel können alle Berechnungen einer Halbiteration in beliebiger Reihenfolge durchgeführt werden, theoretisch ergeben sich für die Berechnung von  $n$  Werten einer Farbe  $n!$  Möglichkeiten. Das direkte Vorgehen, zeilenweise neue Werte zu berechnen, ist durchaus effizient, solange bei Berechnungen die Werte aus der vorhergehenden Zeile noch in der höchsten Cache-Ebene vorhanden sind. Bei zunehmender Zeilenlänge besteht allerdings die Möglichkeit, dass diese Werte zwischenzeitlich in eine tiefere Cache-Ebene oder den Hauptspeicher verdrängt wurden.

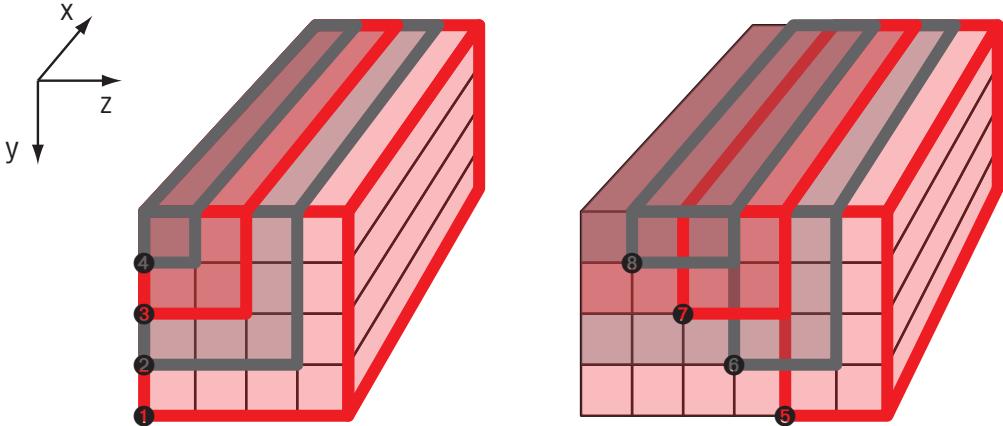

Bei Blocking-Verfahren wird das Gitter gedanklich zerlegt, und die entstehenden Bereiche nacheinander jeweils vollständig abgearbeitet. Im allgemeinen werden hierfür Rechtecke im Zweidimensionalen und Quader im Dreidimensionalen verwendet. Wird die Größe der Blöcke entsprechend der Cache-Hierarchie gewählt, erreicht man hierdurch eine höhere temporale Nähe. Im folgenden zwei einführende Beispiel möglicher Block-Verfahren:

**Beispiel A** Es werden  $1 \times n$  große Blöcke genutzt, also immer Werte aus mehreren Zeilen berechnet.

Die rote Halbiteration beginnt dann mit den Berechnungen im ersten Block, also  $U_{1,1}, U_{1,3} \dots U_{1,y}$  mit  $y \leq n$ . Der Block wird in der Zeile um eins weitergeschoben und  $U_{2,2}, U_{2,4} \dots U_{2,y}$  mit  $y \leq n$  aktualisiert. Dies wird dann bis zum Ende der Zeile und in der nächsten Blockzeile mit dem Block  $U_{1,n+1} - U_{1,2 \cdot n}$  beginnend fortgesetzt. Am unteren Rand des Gitters müssen möglicherweise noch niedrigere Blöcke genutzt werden, wenn die Höhe  $y$  nicht ganzzahlig durch  $n$  teilbar ist. Danach folgt ein analoger Durchgang mit der Berechnung der schwarzen Werte.

**Beispiel B** Es werden  $n \times m$  große Blöcke genutzt. Zunächst wird ein Teil der roten Werte in der ersten Zeile innerhalb  $U_{1,1} - U_{m,1}$  berechnet. Dies wird in den Zeilen darunter fortgesetzt, bis der gesamte Block  $U_{1,1} - U_{m,n}$  berechnet wurde. Der Block wird danach in der Zeile versetzt und mit den roten Werten in  $U_{m+1,1} - U_{2 \cdot m,n}$  fortgefahrene usw. In diesem Fall können am Ende der Zeilen und am unteren Rand verschiedene große Blöcke zum Füllen nötig sein. Die schwarze Halbiteration findet analog statt.

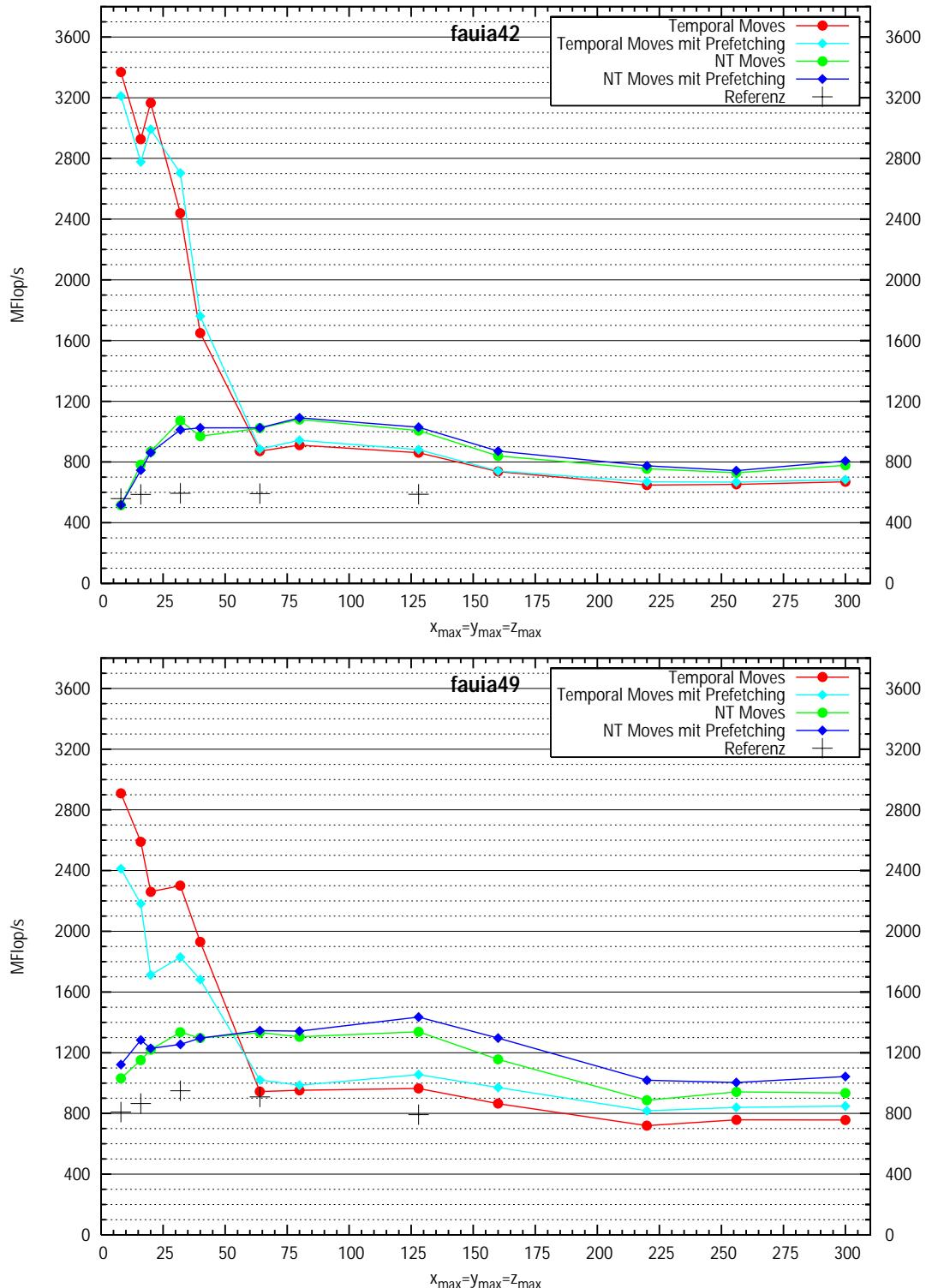

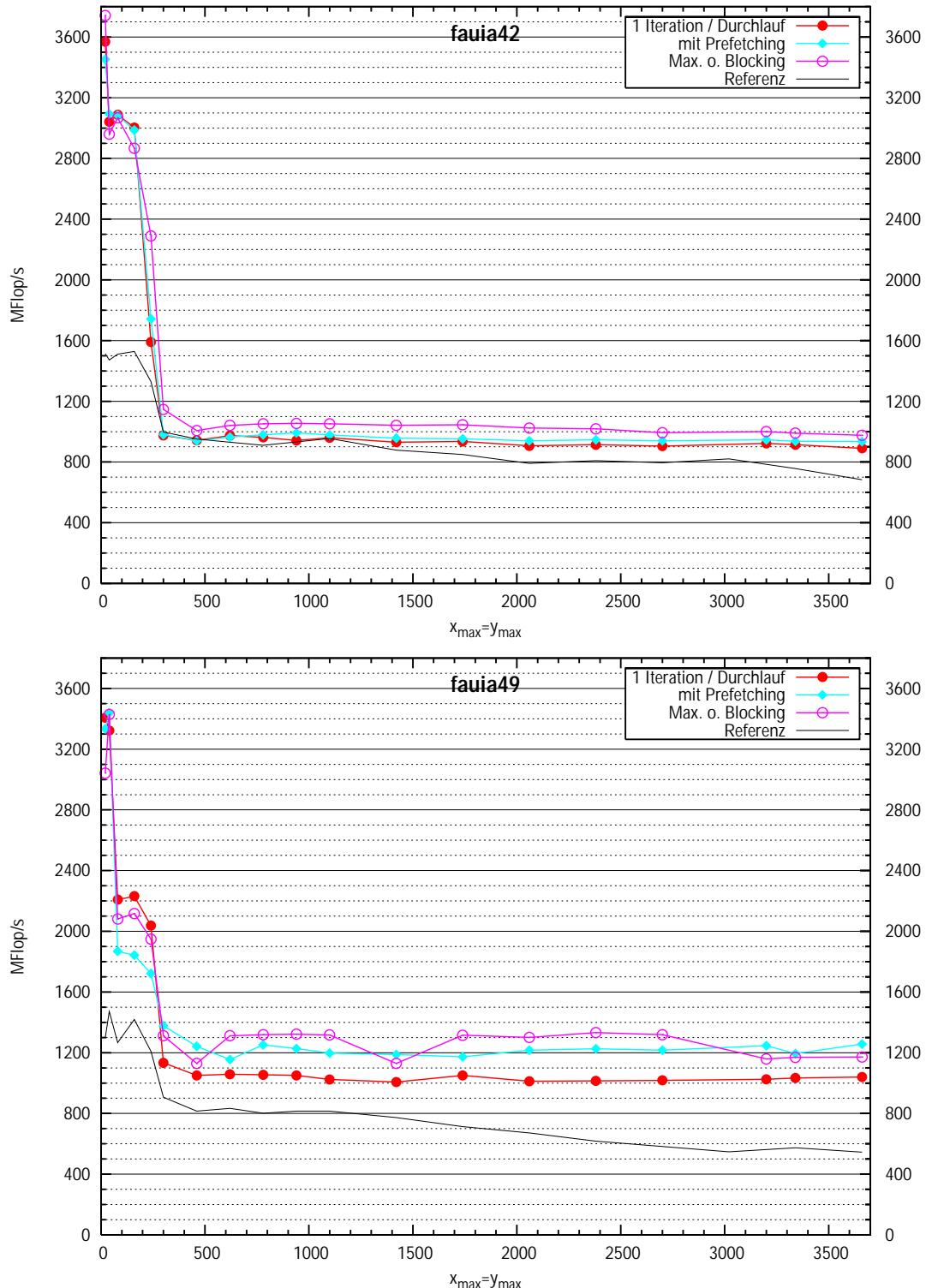

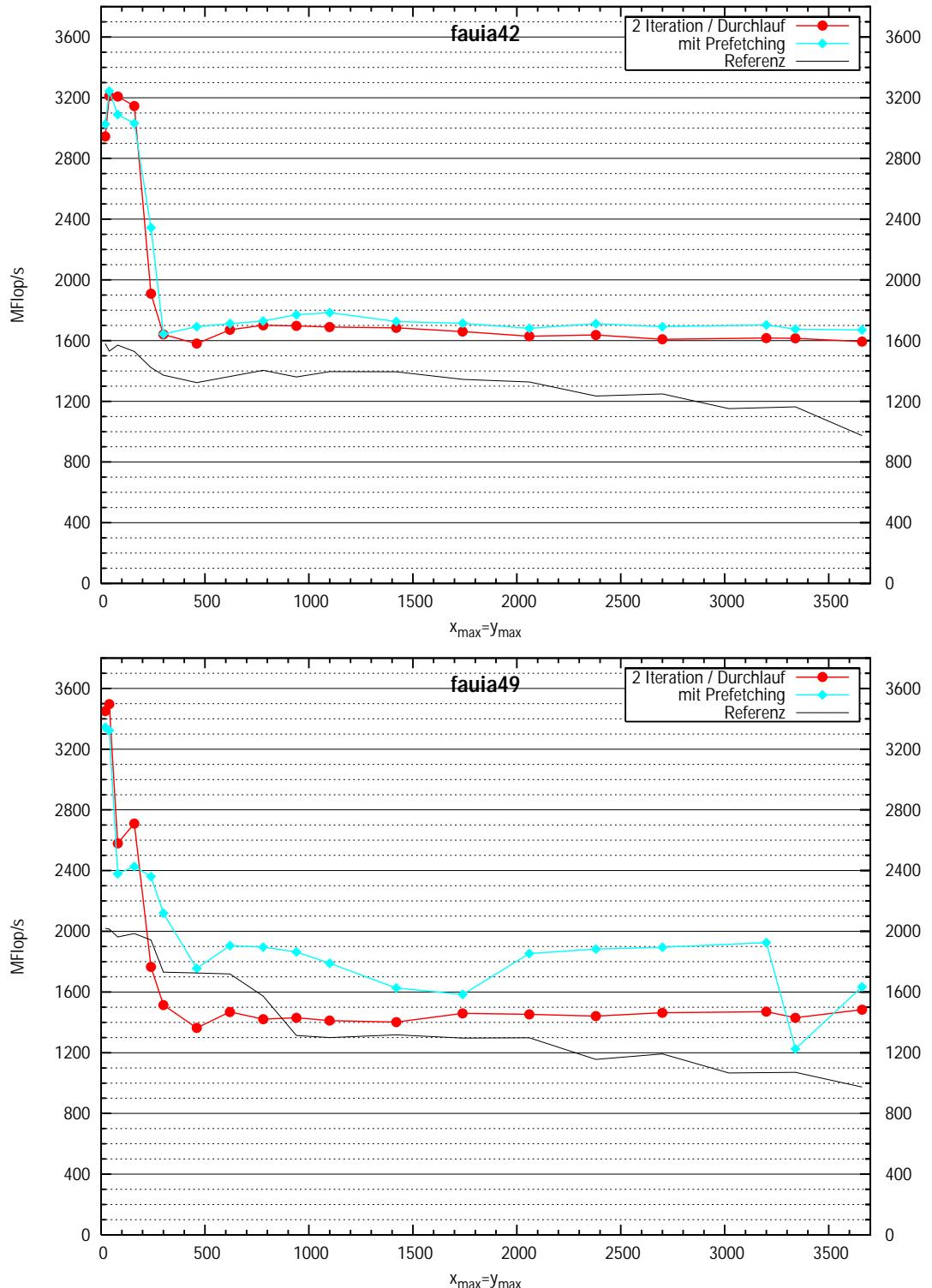

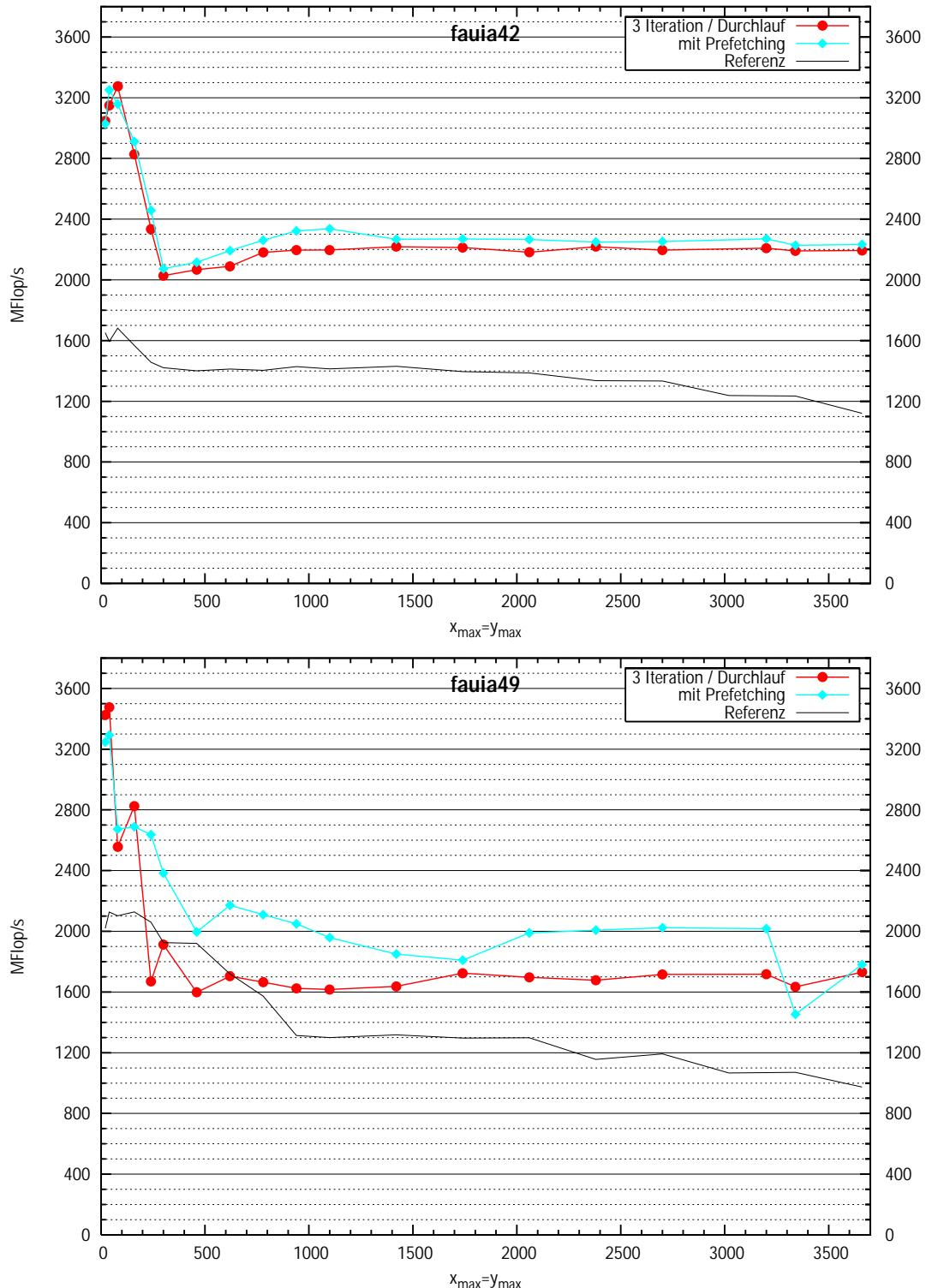

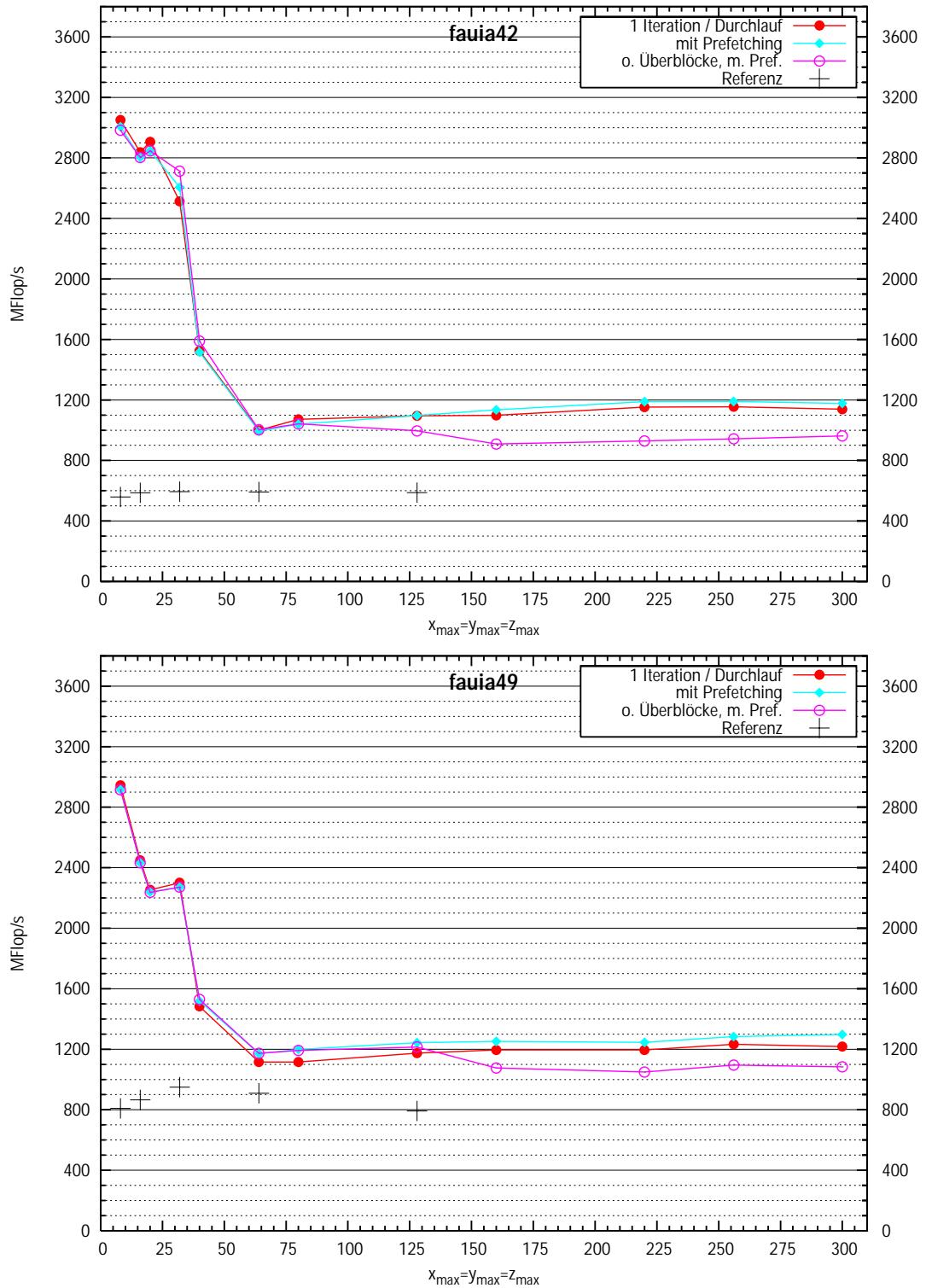

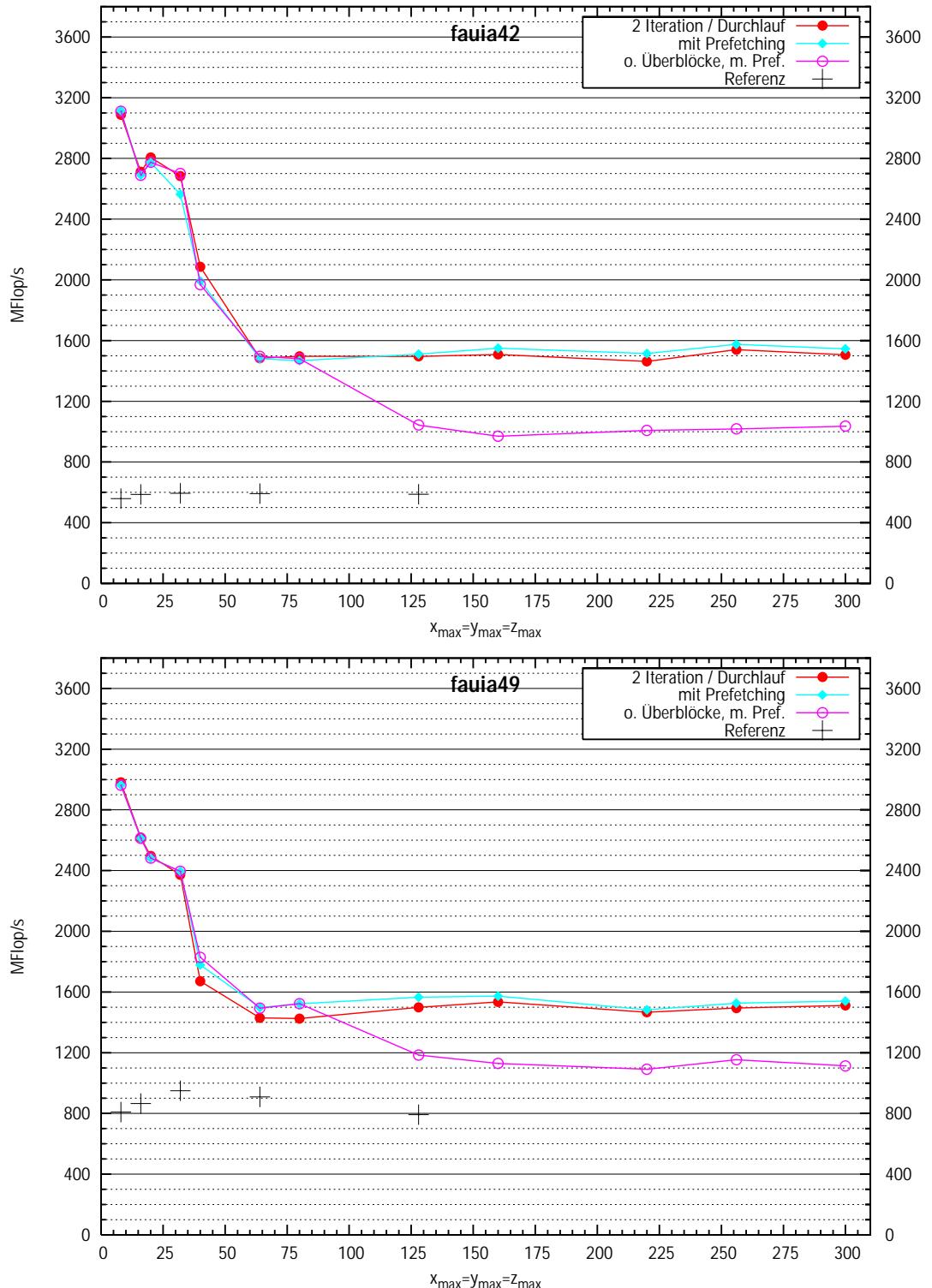

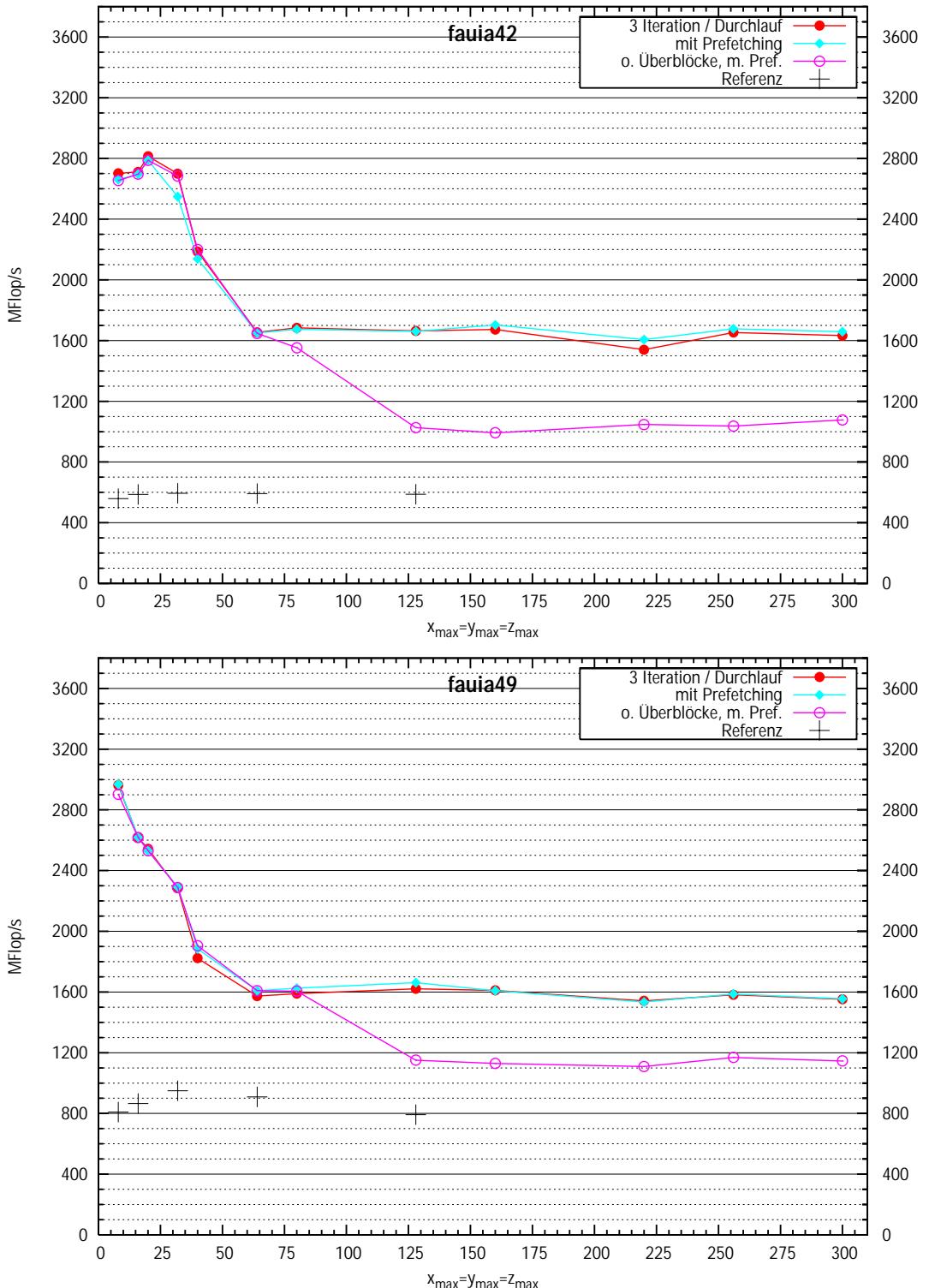

Die genau gewählte Blocking-Technik hängt sehr stark von der ausführenden Hardware ab: Bei niedriger Assoziativität der Caches können Blöcke über viele Zeilen zu Cache-Konflikten führen. Eine Rolle kann auch die Größe des Table Lookaside Buffers spielen, denn Blöcke über mehrere Zeilen greifen auf weiter voneinander im Speicher liegende Adressen zu. Ebenso spielt das Verhalten von Hardware-Prefetchern eine Rolle. Bei einer Berechnung wie in Beispiel A kann dieser häufig keine oder nur scheinbare Datenströme erkennen. Bei Beispiel B kann es zum umgekehrten Effekt kommen: Es werden über die Breite des Blocks hinaus Daten geholt, die bei den Berechnung innerhalb des Blocks wieder verdrängt werden und für den nächsten Block nicht mehr zur Verfügung stehen.