Technische Universität München

Fakultät für Informatik

Diplomarbeit

# **Vervollständigung von Profile-Messungen durch Kombination**

Dietrich Christopeit

## Diplomarbeit

# **Vervollständigung von Profile-Messungen durch Kombination**

Dietrich Christopeit

Aufgabensteller: Prof. Dr. Arndt Bode

Betreuer: Dr. Josef Weidendorfer

Abgabedatum: 15. August 2004

Ich versichere, dass ich diese Diplomarbeit selbstständig verfasst und nur die angegebenen Quellen und Hilfsmittel verwendet habe.

München, den 15. August 2004

Dietrich Christopeit

## **Zusammenfassung**

Bei der Analyse und Erstellung von Programmprofilen von Programmausführungen erlangen Profiling-Tools immer größere Bedeutung. Die Komplexität der modernen Hard- und Software macht die rein manuelle Analyse so gut wie unmöglich. Die modernen Rechensysteme unterstützen den Anwender bei dieser oft schwierigen Aufgabe durch die Bereitstellung von Ereigniszählern, sowohl in den Prozessoren, als auch in Datenstrukturen und Bibliotheken der Betriebssysteme. Die verfügbaren Profiling-Tools lassen sich für die Messung der breiten Vielfalt von Ereignissen bestimmter Ereignistypen konfigurieren und können die gemessenen Werte graphisch darstellen. Viel schneller erlangt der Benutzer so eine Vorstellung, auf welche Programmteile sich die verbrauchten Taktzyklen aufteilen. Zudem ist es möglich, eine reichhaltige Zahl von weiteren Ereignissen messen zu lassen. Solche Ereignisse sind zum Beispiel die Anzahl der fehlerhaft vorhergesagten Verzweigungen. Mit dem Wissen um die Bedeutung dieser gemessenen Werte lassen sich Schwachstellen und Geschwindigkeitsengpässe von Programmen schneller ermitteln, so daß die Lösung für solche Probleme in greifbare Nähe rückt. Die manuelle Analyse des Quellcodes ist bei dem Umfang heutiger Programme kaum erfolgversprechend. Der Erfolg hängt aber auch davon ab, in wie weit der Anwender sich im Klaren über die Zusammenhänge des Auftretens unterschiedlicher Ereignisse unterschiedlicher Ereignistypen ist. Ist diese Basis vorhanden, so kann die Kombination von Ereignistypen einen detaillierteren Einblick in das Verhalten eines Programms in Ausführung liefern, als dies bei der isolierten Betrachtung der aufgetretenen Ereignisse der Fall ist.

# Vorwort

**Über diese Arbeit** Diese Arbeit stellt die Diplomarbeit für den Studiengang Informatik dar und wurde unter der Aufsicht von Dr. Josef Weidendorfer und Prof. Dr. Arndt Bode am Lehrstuhl X für Rechnertechnik und Rechnerorganisation/Parallelrechnerarchitektur der Technischen Universität München verfasst.

Die Arbeit befasst sich mit der Vervollständigung von Profile-Messungen durch die Kombination von Ereignistypen der Hard- und Software. Das Ziel der Arbeit ist die Aufstellung einer allgemeinen Klassifizierung von Ereignistypen, anhand derer die Kombination der Typen verdeutlicht wird. Die vorgeschlagene Klassifizierung wird auf real existente Prozessoren und Betriebssysteme abgebildet, um den angestrebten Überblick am Beispiel zu zeigen. Des weiteren steht die Entwicklung einer abstrakten Spezifikationssprache für die Kombination der Ereignistypen im Blickpunkt dieser Arbeit. Mit Hilfe dieser Sprache soll dem Anwender die Erstellung von Metriken und Heuristiken erleichtert werden. Schließlich wird die Ereignistypkombination in der Praxis angewandt und eine weitere Heuristik für die Berechnung von Inklusiv-/Exklusivkosten von Prozeduraufrufen vorgeschlagen und als Programmmodul für das Visualisierungsprogramm KCachegrind umgesetzt.

**Danksagung** Vor Allem danke ich meinem Professor Prof. Dr. Arndt Bode und meinem Betreuer Dr. Josef Weidendorfer für die Begleitung während der Erstellung dieser Diplomarbeit. Sie machten den Zugang zu Informationen und deren Aufbereitung möglich. Zu buchstäblich jeder Zeit wurde mir bei Problemen geholfen und geduldig jede, auch wiederkehrende Frage beantwortet. Darüber hinaus danke ich meiner Mutter Gabriele von Witzleben-Christopeit und meinem Vater Prof. Dr. Joachim Christopeit für die stete Sorge und geistige Unterstützung meiner Person während dieser Zeit. Nicht nur wurde darauf geachtet, daß alle anders gelagerten Verpflichtungen von mir ferngehalten wurden, auch kam zu jeder Zeit die nötige Aufmunterung. Meinen Kommilitonen und Freunden Alexander Bornschlegl, Evi Groher, Henrik Schmidt, Martin Groher und Stephanie Biller möchte ich im Speziellen einerseits für die fachlich hilfreichen Diskussionen und andererseits für den treuen seelischen Beistand danken.

# Inhaltsverzeichnis

|                                                             |           |

|-------------------------------------------------------------|-----------|

| <b>1 Einleitung</b>                                         | <b>1</b>  |

| 1.1 Aufgabenstellung . . . . .                              | 2         |

| 1.2 Relevante Arbeiten . . . . .                            | 3         |

| 1.3 Aufbau der Arbeit . . . . .                             | 4         |

| <b>2 Performance–Messung – Grundbegriffe und Abgrenzung</b> | <b>5</b>  |

| 2.1 Der Ereignistyp und das Ereignis . . . . .              | 5         |

| 2.1.1 Ereignisarten . . . . .                               | 5         |

| 2.2 Ereignisraten . . . . .                                 | 6         |

| 2.2.1 Event–Rate–Monitoring . . . . .                       | 7         |

| 2.2.2 Cycle–Accounting . . . . .                            | 7         |

| 2.3 Statistisches Sampling . . . . .                        | 8         |

| 2.3.1 Time–Based–Sampling . . . . .                         | 8         |

| 2.3.2 Event–Based–Sampling . . . . .                        | 8         |

| 2.3.3 Präzises attributieren der Samples . . . . .          | 9         |

| 2.4 Codeinstrumentierung . . . . .                          | 10        |

| 2.5 Profiling . . . . .                                     | 10        |

| 2.6 Simulation . . . . .                                    | 11        |

| <b>3 Die Klassifizierung von Ereignistypen</b>              | <b>13</b> |

| 3.1 Hardware . . . . .                                      | 13        |

| 3.1.1 Prozessor . . . . .                                   | 13        |

| 3.1.1.1 Das Interface BRANCH_EVENTS . . . . .               | 15        |

| 3.1.1.2 Die Klasse BRANCH_INSTRUCTIONS . . . . .            | 15        |

| 3.1.1.3 Die Klasse BRANCH_PREDICTION . . . . .              | 17        |

| 3.1.1.4 Die Klasse BRANCH_MISPREDICTED . . . . .            | 17        |

| 3.1.1.5 Die Klasse BRANCH_CORRECT_PREDICTED . . . . .       | 18        |

| 3.1.1.6 Das Interface INSTRUCTION_EXECUTION . . . . .       | 18        |

| 3.1.1.7 Die abstrakte Klasse EPIC_EVENTS . . . . .          | 19        |

| 3.1.1.8 Die Klasse EPIC_INSTRUCTION_ISSUE_AND_RETIREMENT    | 19        |

| 3.1.1.9 Die Klasse EPIC_CONTROL_AND_DATA_SPECULATION . . .  | 20        |

| 3.1.1.10 Die Klasse FP_EXECUTION . . . . .                  | 23        |

| 3.1.1.11 Die Klasse INTEGER_EXECUTION . . . . .             | 23        |

| 3.1.1.12 Die Klasse GENERAL_EXECUTION . . . . .             | 24        |

| 3.1.1.13 Die Klasse MEMORY_EVENTS . . . . .                 | 25        |

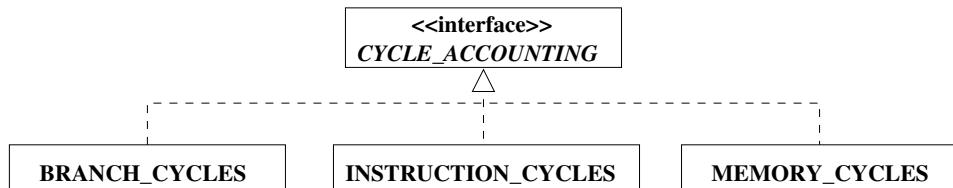

| 3.1.1.14 Das Interface CYCLE_ACCOUNTING . . . . .           | 26        |

| 3.1.1.15 Die Klasse BRANCH_CYCLES . . . . .                 | 27        |

| 3.1.1.16 Die Klasse INSTRUCTION_CYCLES . . . . .            | 27        |

|          |                                                    |           |

|----------|----------------------------------------------------|-----------|

| 3.1.1.17 | Die Klasse MEMORY_CYCLES . . . . .                 | 28        |

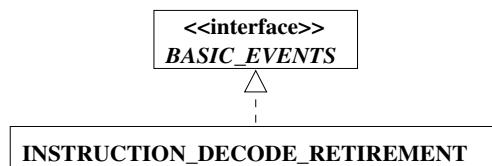

| 3.1.1.18 | Das Interface BASIC_EVENTS . . . . .               | 28        |

| 3.1.1.19 | Die Klasse INSTRUCTION_DECODE_RETIREMENT . . . . . | 29        |

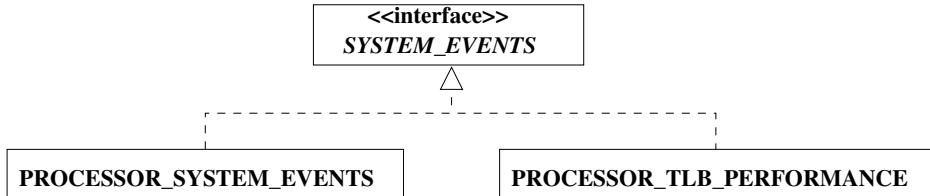

| 3.1.1.20 | Das Interface SYSTEM_EVENTS . . . . .              | 29        |

| 3.1.1.21 | Die Klasse PROCESSOR_SYSTEM_EVENTS . . . . .       | 30        |

| 3.1.1.22 | Die Klasse PROCESSOR_TLB_PERFORMANCE . . . . .     | 31        |

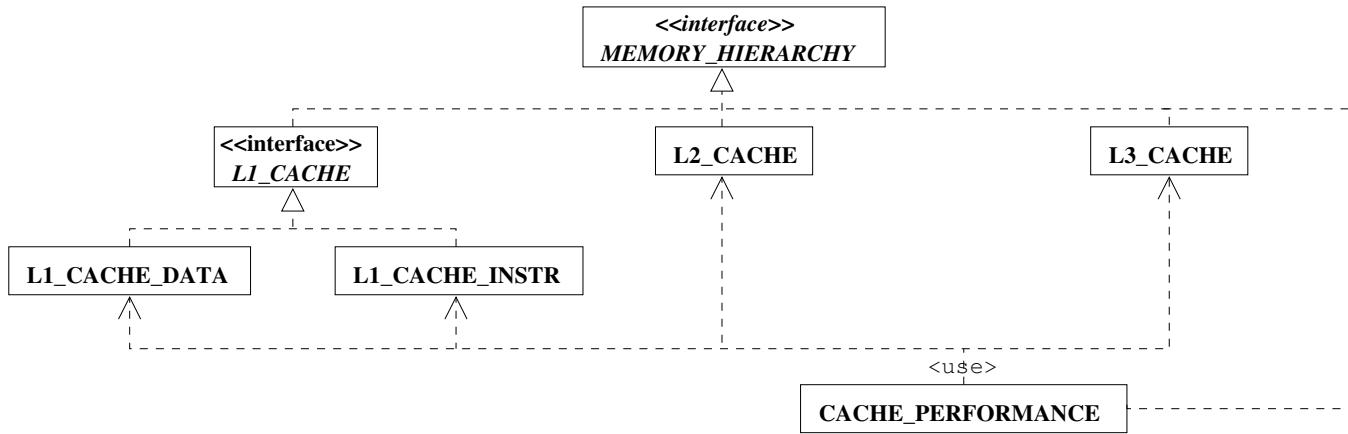

| 3.1.1.23 | Das Interface MEMORY_HIERARCHY . . . . .           | 32        |

| 3.1.1.24 | Das Interface L1_CACHE . . . . .                   | 33        |

| 3.1.1.25 | Die Klasse L1_CACHE_DATA . . . . .                 | 33        |

| 3.1.1.26 | Die Klasse L1_CACHE_INSTR . . . . .                | 33        |

| 3.1.1.27 | Die Klasse L2_CACHE . . . . .                      | 34        |

| 3.1.1.28 | Die Klasse L3_CACHE . . . . .                      | 35        |

| 3.1.1.29 | Die Klasse CACHE_PERFORMANCE . . . . .             | 36        |

| 3.1.2    | Prozessorexterner Speicher . . . . .               | 36        |

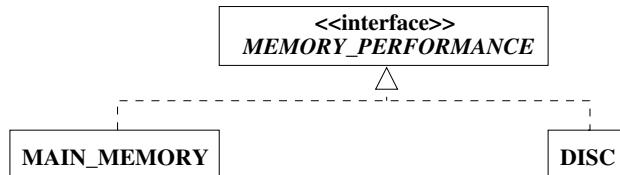

| 3.1.2.1  | Das Interface MEMORY_PERFORMANCE . . . . .         | 37        |

| 3.1.2.2  | Die Klasse MAIN_MEMORY . . . . .                   | 37        |

| 3.1.2.3  | Die Klasse DISC . . . . .                          | 38        |

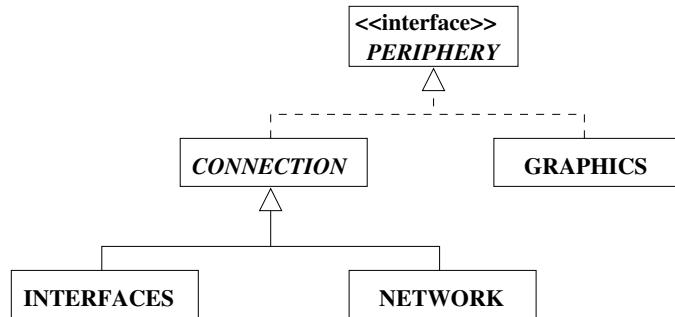

| 3.1.3    | Peripherie . . . . .                               | 38        |

| 3.1.3.1  | Die abstrakte Klasse CONNECTION . . . . .          | 39        |

| 3.1.3.2  | Die Klasse NETWORK . . . . .                       | 39        |

| 3.1.3.3  | Die Klasse INTERFACES . . . . .                    | 40        |

| 3.1.3.4  | Die Klasse GRAPHICS . . . . .                      | 40        |

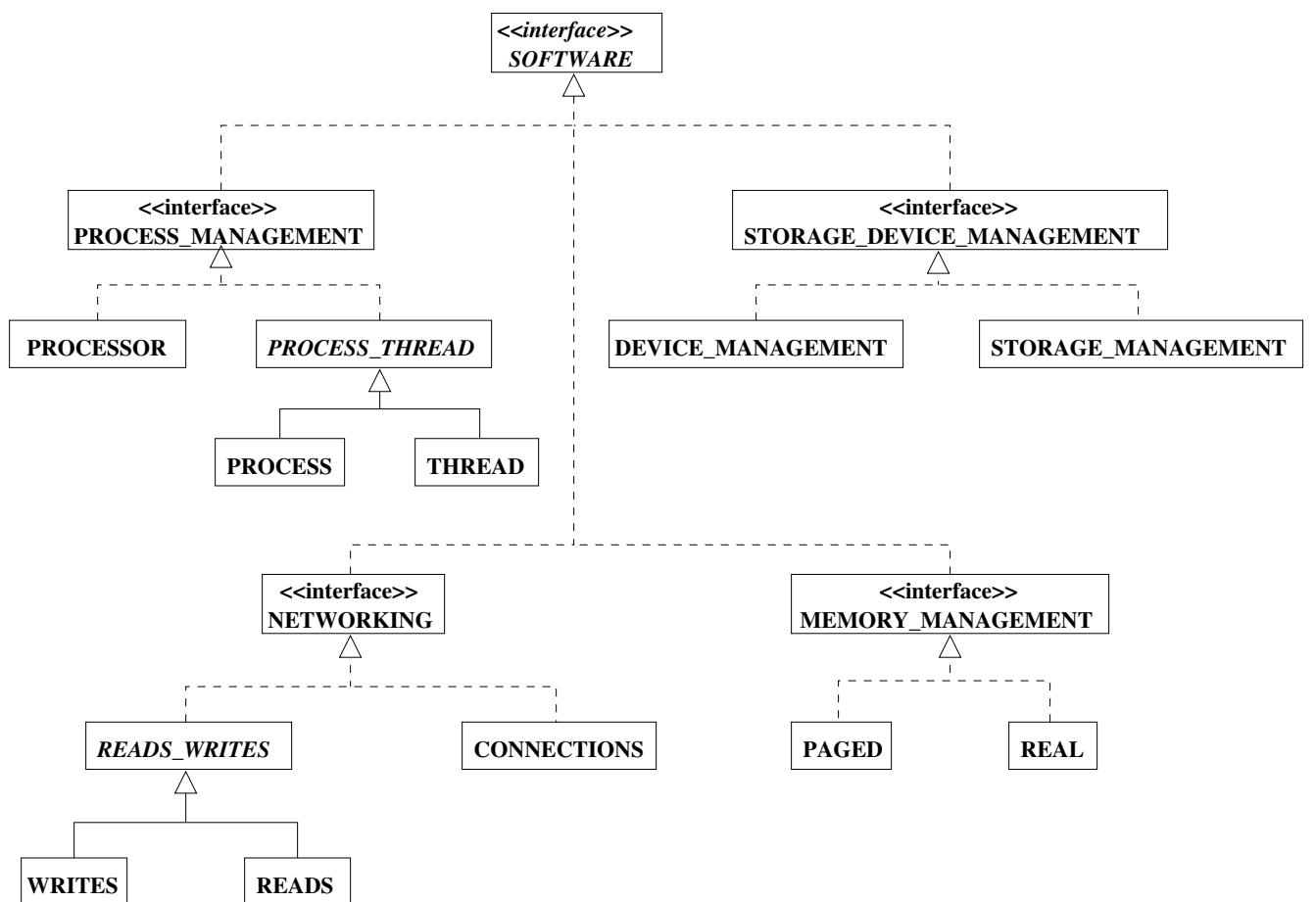

| 3.2      | Software . . . . .                                 | 40        |

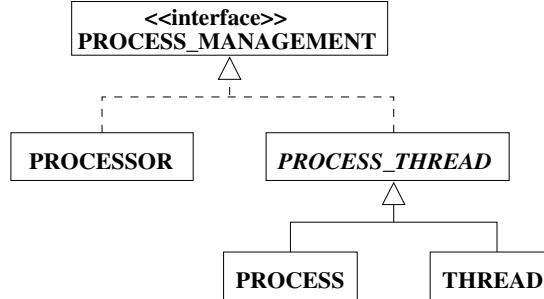

| 3.2.1    | Das Interface PROCESS_MANAGEMENT . . . . .         | 41        |

| 3.2.1.1  | Die Klasse PROCESSOR . . . . .                     | 42        |

| 3.2.1.2  | Die abstrakte Klasse PROCESS_THREAD . . . . .      | 43        |

| 3.2.1.3  | Die Klasse PROCESS . . . . .                       | 44        |

| 3.2.1.4  | Die Klasse THREAD . . . . .                        | 44        |

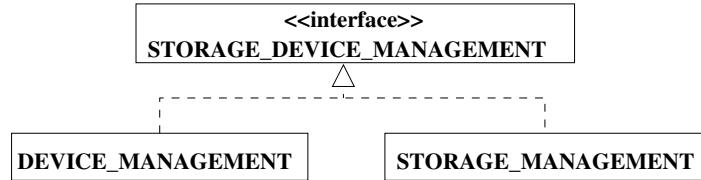

| 3.2.2    | Das Interface STORAGE_DEVICE_MANAGEMENT . . . . .  | 44        |

| 3.2.2.1  | Die Klasse DEVICE_MANAGEMENT . . . . .             | 45        |

| 3.2.2.2  | Die Klasse STORAGE_MANAGEMENT . . . . .            | 45        |

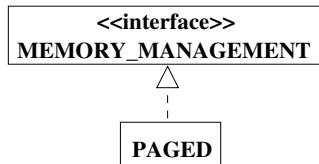

| 3.2.3    | Das Interface MEMORY_MANAGEMENT . . . . .          | 46        |

| 3.2.3.1  | Die Klasse PAGED . . . . .                         | 46        |

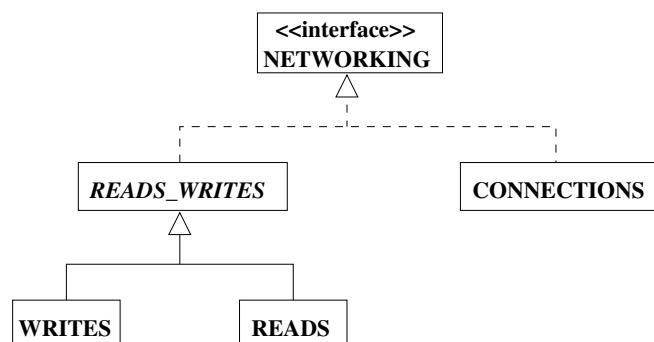

| 3.2.4    | Das Interface NETWORKING . . . . .                 | 47        |

| 3.2.4.1  | Die abstrakte Klasse READS_WRITES . . . . .        | 48        |

| 3.2.4.2  | Die Klasse READS . . . . .                         | 48        |

| 3.2.4.3  | Die Klasse WRITES . . . . .                        | 48        |

| 3.2.4.4  | Die Klasse CONNECTIONS . . . . .                   | 48        |

| <b>4</b> | <b>Implementierung der Klassen</b>                 | <b>50</b> |

| 4.1      | Vorstellung der betrachteten Prozessoren . . . . . | 50        |

| 4.1.1    | Intel IA-64 Itanium . . . . .                      | 50        |

| 4.1.1.1  | Die Performance Counter Register . . . . .         | 51        |

| 4.1.1.2  | Überlauf des Ereigniszählers . . . . .             | 51        |

| 4.1.1.3  | Ereignisqualifizierung . . . . .                   | 52        |

| 4.1.2    | Intel IA-32 P6 . . . . .                           | 53        |

| 4.1.2.1  | Die Performance Counter Register . . . . .         | 54        |

|          |                                                                                              |           |

|----------|----------------------------------------------------------------------------------------------|-----------|

| 4.1.2.2  | Überlauf des Ereigniszählers . . . . .                                                       | 54        |

| 4.1.2.3  | Ereignisqualifizierung . . . . .                                                             | 54        |

| 4.1.3    | IBM RISC PowerPC 604e . . . . .                                                              | 55        |

| 4.1.3.1  | Die Performance Counter Register . . . . .                                                   | 55        |

| 4.1.3.2  | Überlauf des Ereigniszählers . . . . .                                                       | 55        |

| 4.1.3.3  | Ereignisqualifizierung . . . . .                                                             | 55        |

| 4.2      | Implementierung der Klassifizierung in den betrachteten Prozessoren . . . . .                | 56        |

| 4.3      | Verfügbarkeit der Ereignistypen der übrigen Hardware . . . . .                               | 56        |

| 4.3.1    | Das Interface MEMORY_PERFORMANCE . . . . .                                                   | 56        |

| 4.3.1.1  | Die Klasse MAIN_MEMORY . . . . .                                                             | 56        |

| 4.3.1.2  | Die Klasse DISC . . . . .                                                                    | 56        |

| 4.3.2    | Das Interface PERIPHERY . . . . .                                                            | 57        |

| 4.3.2.1  | Die abstrakte Klasse CONNECTION . . . . .                                                    | 57        |

| 4.3.2.2  | Die Klasse Graphics . . . . .                                                                | 57        |

| 4.4      | Vorstellung der betrachteten Betriebssysteme . . . . .                                       | 57        |

| 4.4.1    | Windows 2000 . . . . .                                                                       | 57        |

| 4.4.2    | Linux . . . . .                                                                              | 58        |

| 4.5      | Implementierung der Klassifizierung in den Betriebssystemen Windows 2000 und Linux . . . . . | 58        |

| <b>5</b> | <b>Die Spezifikation abgeleiteter Ereignisse</b>                                             | <b>59</b> |

| 5.1      | Entwurf . . . . .                                                                            | 59        |

| 5.1.1    | Ereignismengen und Ereignisströme . . . . .                                                  | 59        |

| 5.1.1.1  | Ereignismengen . . . . .                                                                     | 60        |

| 5.2      | Sprachdefinition von DESL . . . . .                                                          | 60        |

| 5.2.1    | Spezifikationsstruktur in DESL . . . . .                                                     | 61        |

| 5.2.2    | Datentypen in DESL . . . . .                                                                 | 62        |

| 5.2.3    | Recorddefinition . . . . .                                                                   | 63        |

| 5.2.4    | Definition eines Filters . . . . .                                                           | 65        |

| 5.2.5    | Konstanten- und Basisereignisdefinition . . . . .                                            | 67        |

| 5.3      | Beispiele in DESL . . . . .                                                                  | 67        |

| <b>6</b> | <b>Anwendung</b>                                                                             | <b>71</b> |

| 6.1      | Die Berechnung der Inklusiv-/Exklusivkosten bei Prozeduraufrufen . . . . .                   | 71        |

| 6.2      | Die Heuristik von gprof . . . . .                                                            | 73        |

| 6.3      | Eine alternative Heuristik – die Quotientenheuristik . . . . .                               | 76        |

| 6.4      | Vergleich der Heuristiken . . . . .                                                          | 80        |

| 6.4.1    | Qualitätsmaß für den Vergleich der Ergebnisse . . . . .                                      | 80        |

| <b>7</b> | <b>Zusammenfassung</b>                                                                       | <b>84</b> |

| 7.1      | Ergebnisse . . . . .                                                                         | 84        |

| 7.1.1    | Ergebnisse der Klassifizierung von Ereignistypen . . . . .                                   | 85        |

| 7.1.2    | Ergebnisse der Spezifikationssprache DESL . . . . .                                          | 85        |

| 7.1.3    | Ergebnisse der Implementierung der Quotientenheuristik . . . . .                             | 86        |

| 7.2      | Ausblick . . . . .                                                                           | 87        |

| 7.2.1    | Klassifizierung der Ereignistypen . . . . .                                                  | 87        |

| 7.2.2    | DESL . . . . .                                                                               | 88        |

|          |                                                            |            |

|----------|------------------------------------------------------------|------------|

| 7.2.3    | Quotientenheuristik                                        | 88         |

| <b>A</b> | <b>Klassifizierung der Ereignistypen</b>                   | <b>91</b>  |

| A.1      | Hardware                                                   | 91         |

| A.2      | Software                                                   | 91         |

| <b>B</b> | <b>Realisierung der Ereignistypklassen in der Hardware</b> | <b>93</b>  |

| B.1      | Prozessoren                                                | 93         |

| B.1.1    | Das Interface BRANCH_EVENTS                                | 93         |

| B.1.1.1  | Die Klasse BRANCH_INSTRUCTIONS                             | 93         |

| B.1.1.2  | Die Klasse BRANCH_PREDICTION                               | 93         |

| B.1.1.3  | Die Klasse BRANCH_MISPREDICTED                             | 94         |

| B.1.1.4  | Die Klasse BRANCH_CORRECT_PREDICTED                        | 94         |

| B.1.2    | Das Interface INSTRUCTION_EXECUTION                        | 94         |

| B.1.2.1  | Die Klasse EPIC_EVENTS                                     | 95         |

| B.1.2.2  | Die Klasse GENERAL_EXECUTION                               | 95         |

| B.1.2.3  | Die Klasse INTEGER_EXECUTION                               | 95         |

| B.1.2.4  | Die Klasse FP_EXECUTION                                    | 95         |

| B.1.2.5  | Die Klasse MEMORY_EVENTS                                   | 96         |

| B.1.3    | Das Interface CYCLE_ACCOUNTING                             | 96         |

| B.1.3.1  | Die Klasse BRANCH_CYCLES                                   | 96         |

| B.1.3.2  | Die Klasse INSTRUCTION_CYCLES                              | 97         |

| B.1.3.3  | Die Klasse MEMORY_CYCLES                                   | 97         |

| B.1.4    | Das Interface BASIC_EVENTS                                 | 97         |

| B.1.4.1  | Die Klasse INSTRUCTION_DECODE_AND_RETIREMENT               | 98         |

| B.1.5    | Das Interface SYSTEM_EVENTS                                | 98         |

| B.1.5.1  | Die Klasse PROCESSOR_SYSTEM_EVENTS                         | 98         |

| B.1.5.2  | Die Klasse TLB_PERFORMANCE                                 | 98         |

| B.1.6    | Das Interface MEMORY_HIERARCHY                             | 98         |

| B.1.6.1  | Die Klassen L1_CACHE_DATA und L1_CACHE_INSTR               | 99         |

| B.1.6.2  | Die Klasse L2_CACHE                                        | 99         |

| B.1.6.3  | Die Klasse L3_CACHE                                        | 99         |

| B.1.6.4  | Die Klasse CACHE_PERFORMANCE                               | 100        |

| <b>C</b> | <b>Realisierung der Ereignistypklassen in der Software</b> | <b>103</b> |

| C.1      | Das Interface PROCESS_MANAGEMENT                           | 103        |

| C.1.1    | Die Klasse Processor                                       | 103        |

| C.1.2    | Die abstrakte Klasse PROCESS_THREAD                        | 103        |

| C.1.3    | Die Klasse PROCESS                                         | 104        |

| C.1.4    | Die Klasse THREAD                                          | 104        |

| C.2      | Das Interface STORAGE_DEVICE_MANAGEMENT                    | 104        |

| C.2.1    | Die Klasse DEVICE_MANAGEMENT                               | 104        |

| C.2.2    | Die Klasse STORAGE_MANAGEMENT                              | 105        |

| C.3      | Das Interface MEMORY_MANAGEMENT                            | 105        |

| C.3.1    | Die Klasse PAGED                                           | 105        |

| C.3.2    | Das Interface NETWORKING                                   | 106        |

| C.3.2.1  | Die abstrakte Klasse READS_WRITES                          | 106        |

*Inhaltsverzeichnis*

---

|                                                             |            |

|-------------------------------------------------------------|------------|

| C.3.2.2 Die Klasse CONNECTIONS . . . . .                    | 106        |

| <b>D Beispielprogramm für den Vergleich der Heuristiken</b> | <b>107</b> |

| <b>E Glossar</b>                                            | <b>110</b> |

| <b>Literaturverzeichnis</b>                                 | <b>113</b> |

# Abbildungsverzeichnis

|      |                                                                                                     |    |

|------|-----------------------------------------------------------------------------------------------------|----|

| 2.1  | Die Recordstruktur für präzises Sampling. . . . .                                                   | 10 |

| 3.1  | CISC-Prozessor, IA-32 Pentium . . . . .                                                             | 14 |

| 3.2  | Klassenhierarchie BRANCH_EVENTS . . . . .                                                           | 16 |

| 3.3  | Klassenhierarchie INSTRUCTION_EXECUTION . . . . .                                                   | 18 |

| 3.4  | Datenspekulation . . . . .                                                                          | 21 |

| 3.5  | Klassenhierarchie CYCLE_ACCOUNTING . . . . .                                                        | 26 |

| 3.6  | Klassenhierarchie BASIC_EVENTS . . . . .                                                            | 28 |

| 3.7  | Klassenhierarchie SYSTEM_EVENTS . . . . .                                                           | 30 |

| 3.8  | Klassenhierarchie MEMORY_HIERARCHY . . . . .                                                        | 33 |

| 3.9  | Klassenhierarchie MEMORY_PERFORMANCE . . . . .                                                      | 37 |

| 3.10 | Klassenhierarchie PERIPHERY . . . . .                                                               | 39 |

| 3.11 | Struktur eines Betriebssystems . . . . .                                                            | 41 |

| 3.12 | Klassenhierarchie PROCESS_MANAGEMENT . . . . .                                                      | 42 |

| 3.13 | Klassenhierarchie STORAGE_DEVICE_MANAGEMENT . . . . .                                               | 45 |

| 3.14 | Klassenhierarchie MEMORY_MANAGEMENT . . . . .                                                       | 46 |

| 3.15 | Klassenhierarchie NETWORKING . . . . .                                                              | 47 |

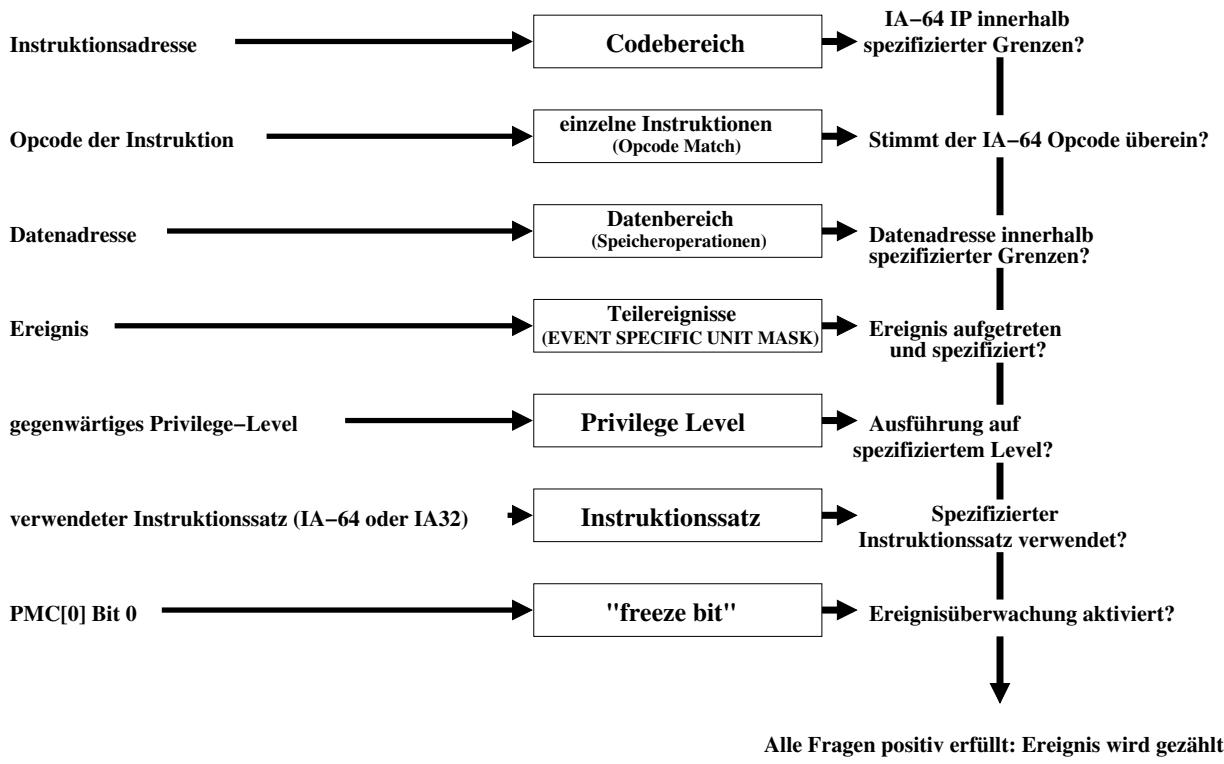

| 4.1  | Ereignisqualifizierung Intel Itanium . . . . .                                                      | 53 |

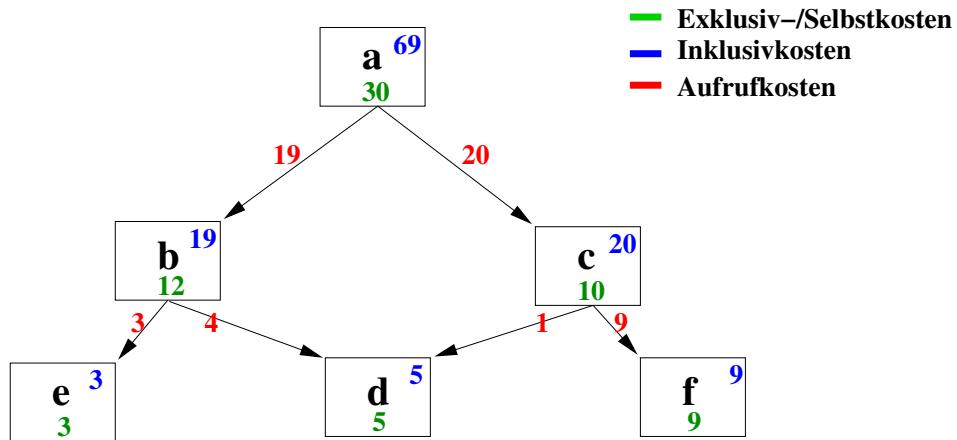

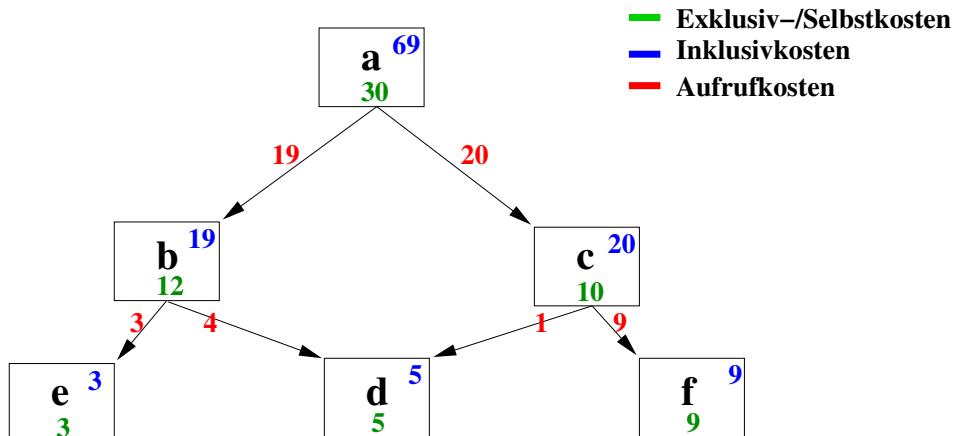

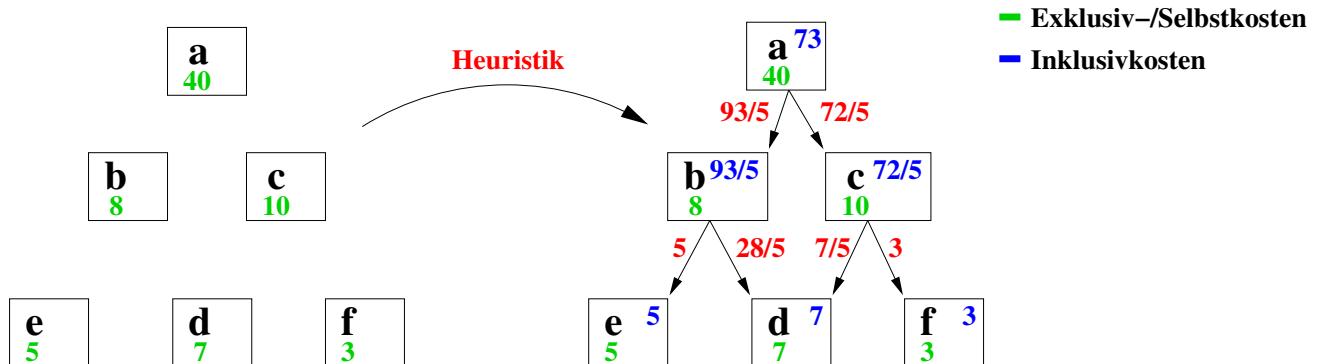

| 6.1  | Ein Aufrufbaum für Prozeduren a, b, c, d, e und f. . . . .                                          | 72 |

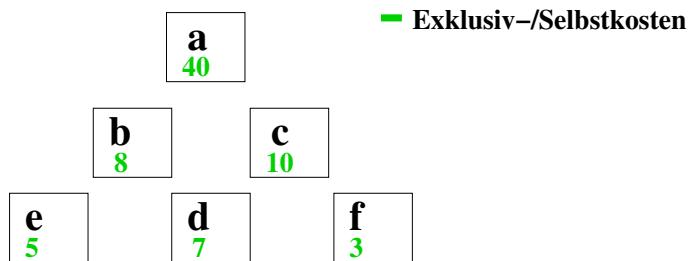

| 6.2  | Die Meßergebnisse für Prozeduren a, b, c, d, e und f nach Abschluß des Samplings. . . . .           | 76 |

| 6.3  | Die Meßergebnisse für Prozeduren a, b, c, d, e und f nach Abschluß eines Simulationslaufes. . . . . | 76 |

| 6.4  | Die durch die Heuristik angereicherten Daten des Samplings. . . . .                                 | 78 |

| 6.5  | Der zentrale Aufrufbaum des Beispielprogramms. . . . .                                              | 82 |

| A.1  | Klassenhierarchie Hardware . . . . .                                                                | 91 |

| A.2  | Klassenhierarchie Software . . . . .                                                                | 92 |

# Tabellenverzeichnis

|                                                                                   |     |

|-----------------------------------------------------------------------------------|-----|

| 3.1 Cache–Raten für den L1–, L2– und L3–Cache. . . . .                            | 37  |

| 6.1 Quotientenberechnung Aufrufkosten/Inklusivkosten . . . . .                    | 77  |

| 6.2 Vermittels Heuristik angereicherte Inklusivkosten des Samplinglaufes. . . . . | 77  |

| 6.3 Datenschema der Simulationsdaten für DESL–Spezifikation . . . . .             | 78  |

| 6.4 Datenschema der Sampling–Daten für DESL–Spezifikation . . . . .               | 79  |

| 6.5 Quotientenberechnung in DESL für die Quotientenheuristik . . . . .            | 80  |

| 6.6 Gemessene und berechnete Inklusivkosten . . . . .                             | 82  |

| 6.7 Qualität der Heuristiken . . . . .                                            | 83  |

| B.1 Implementierung der Klasse BRANCH_INSTRUCTIONS . . . . .                      | 94  |

| B.2 Implementierung der Klasse BRANCH_PREDICTION . . . . .                        | 94  |

| B.3 Implementierung der Klasse BRANCH_MISPREDICTED . . . . .                      | 94  |

| B.4 Implementierung der Klasse GENERAL_EXECUTION . . . . .                        | 95  |

| B.5 Implementierung der Klasse INTEGER_EXECUTION . . . . .                        | 95  |

| B.6 Implementierung der Klasse FP_EXECUTION . . . . .                             | 96  |

| B.7 Implementierung der Klasse MEMORY_EVENTS . . . . .                            | 96  |

| B.8 Implementierung der Klasse BRANCH_CYCLES . . . . .                            | 97  |

| B.9 Implementierung der Klasse INSTRUCTION_CYCLES . . . . .                       | 97  |

| B.10 Implementierung der Klasse MEMORY_CYCLES . . . . .                           | 97  |

| B.11 Implementierung der Klasse INSTRUCTION_DECODE_AND_RETIREMENT . .             | 98  |

| B.12 Implementierung der Klasse PROCESSOR_SYSTEM_EVENTS . . . . .                 | 99  |

| B.13 Implementierung der Klasse TLB_PERFORMANCE . . . . .                         | 100 |

| B.14 Implementierung der Klassen L1_CACHE_DATA und L1_CACHE_INSTR . .             | 100 |

| B.15 Implementierung der Klasse L2_CACHE . . . . .                                | 101 |

| B.16 Implementierung der Klasse CACHE_PERFORMANCE . . . . .                       | 102 |

| C.1 Implementierung der Klasse PROCESSOR . . . . .                                | 103 |

| C.2 Implementierung der Klasse PROCESS_THREAD . . . . .                           | 104 |

| C.3 Implementierung der Klasse THREAD . . . . .                                   | 104 |

| C.4 Implementierung der Klasse DEVICE_MANAGEMENT . . . . .                        | 105 |

| C.5 Implementierung der Klasse STORAGE_MANAGEMENT . . . . .                       | 105 |

| C.6 Implementierung der Klasse READS_WRITES . . . . .                             | 106 |

| C.7 Implementierung der Klasse CONNECTIONS . . . . .                              | 106 |

# 1 Einleitung

Der Grad der Komplexität von Mikroprozessoren folgt seit 1965 der Regel von Moore und Noyce, die besagt, dass sich die Anzahl der auf einem integrierten Halbleiterbaustein befindlichen Transistorfunktionen etwa alle 18 bis 24 Monate verdoppelt [11]. Hatte der Intel Prozessor 8080 des Jahres 1972 noch 3500 Transistoren, so waren es 1974 schon 6000 Transistoren und mit der Einführung des Pentium Prozessors im Jahre 1993 sogar schon 3,1 Million. Über diese Zeit hinweg wurde immer wieder prognostiziert, daß die Entwicklung der Mooreschen Vorhersage nicht mehr folgen könne, da technische Grenzen erreicht seien; doch Antworten zum Beispiel auf Probleme bezüglich der Isolation zwischen den Leiterbahnen, Kühlung der Prozessoren, oder der Genauigkeit der Laser, die zum Ätzen der Schaltkreise verwendet werden, wurden immer gefunden. Viele Gründe geben also den Anlass, zu vermuten, daß Moores Gesetz nicht mehr für lange Zeit seine Gültigkeit behalten können wird, Moore selbst zweifelt dies an. Doch der technologische Fortschritt scheint nicht zu bremsen zu sein und so werden wohl am ehesten kühle wirtschaftliche Argumente den Trend ändern [25].

Der steigende Integrationsgrad der Prozessoren wurde auf der Seite der Software von immer größer werdenden Programmen begleitet. Das Betriebssystem Windows 3.1 aus dem Jahr 1990 der Firma Microsoft hatte drei Millionen Source Lines of Code (SLOC), Windows NT des Jahres 1995 benötigte vier Millionen SLOC und Windows 95 bestand mit der Einführung 1997 aus 15 Millionen SLOC, also mehr doppelt so viel wie Windows 3.1 und NT aus den Jahren zuvor zusammen. Debian GNU/Linux 2.2 vom August 2000 bestand sogar aus 55 Millionen SLOC, hätte 14005 Personenjahre für die Entwicklung benötigt und ein Budget 1,9 Milliarden US-Dollar verbraucht [37].

Angesichts der steigenden Komplexität auf den beiden Seiten der elektronischen Informationsverarbeitung ist die Geschwindigkeit eines Programms ein zentrales Thema. Immer größere Programme scheinen immer schnellere Prozessoren zu brauchen, um mit diesen immer komplexere Probleme in immer kürzerer Zeit lösen zu können. Auch wenn Programme für beispielsweise die Wettervorhersage nicht derartig viele Codezeilen haben, so sind die Verursacher für Geschwindigkeitsprobleme schwer im Code zu lokalisieren; und die Performance eines Programms ist mit das wichtigste Verkaufsargument.

Dieser Tatsache sind sich auch die Prozessorhersteller bewusst geworden und haben zum Beispiel mit der Einführung des Pentium dem Programmierer viele Möglichkeiten an die Hand gegeben, um Performance-Probleme im Programm aufzuspüren zu können. So finden sich dort Zähler, die zum Beispiel die Anzahl der L1-Cache-Misses und das Auftreten ähnlicher Ereignisse anzeigen. Solche Zähler können so programmiert werden, daß mit Erreichen eines bestimmten Wertes ein Interrupt ausgelöst wird, welcher durch Software bearbeitet werden kann. So werden statistische Erhebungen über das Ablaufverhalten von Programmen und die Erstellung eines Ablaufprofils möglich gemacht. Zusätzlich im Source-Code an geeigneten Stellen eingefügte Codefragmente, die Aufschluß über zum Beispiel das Auf-

rufverhalten von Prozeduren liefern, helfen das Geschwindigkeitsproblem bis zur Lösung immer weiter einzugrenzen. Dieses, als Instrumentierung bezeichnete Verfahren setzt aber, im Gegensatz zur Ereignismessung im Prozessor, die Verfügbarkeit des Quellcodes voraus. Sind die Daten aus Hard- und Software gesammelt, so geben Visualisierungsprogramme wie KCachegrind [1] oder VTune [24] in Histogrammen und Kurven ein Bild vom Verhalten des ablaufenden Programms über seine Ausführungszeit hinweg.

### 1.1 Aufgabenstellung

Wie oben angesprochen, ist es auf Grund der hohen Komplexität heutiger Prozessoren und Programme schwierig, Software zu beschleunigen. Zwar würden schnellere Prozessoren für gewisse Zeit langsamem Programmen auf die Sprünge helfen, doch kann die stetige Anschaffung modernerer Hardware nicht die Lösung sein. Viele Punkte gibt es, an denen der Programmierer ansetzen kann, ein Performance-Problem zu lösen. Von schnelleren Algorithmen, bis hin zu einer optimierten Speicherverwaltung führt der Weg, um dem Anwender Zeit zu ersparen. Dabei wird der Benutzer und der Entwickler durch eine Vielzahl von Werkzeugen unterstützt, die Auskunft über das Laufzeitverhalten geben [33].

Die Aufgabenstellung beinhaltet die Erstellung einer Klassifizierung von Ereignistypen, die für die Performance-Analyse von Belang ist. Die erste Unterscheidung wird zwischen Hardware und Software getroffen.

Im Hinblick auf die Hardware wird untersucht, welche Ereignisse im Prozessor und in der Peripherie auftreten und gemessen werden können. Eine Klassifizierung der Typen dieser Ereignisse gibt dann einen geordneten Gesamtüberblick, der auch die Beziehungen zwischen einzelnen Ereignistypklassen verdeutlicht. Angestrebt ist ein einheitliches Modell, welches unabhängig von der Architektur, die Vielzahl der verschiedenen Ereignistypen zusammenfasst, die in den Referenzhandbüchern der Prozessorhersteller nur schwer und meist ungeordnet zu finden sind. Das vorgeschlagene Modell wird anhand konkreter Architekturen auf Praktikabilität untersucht, nämlich auf die CISC-Architektur IA-32 P6 [3], die 64 Bit VLIW/EPIC Architektur IA-64 Itanium [6] der Firma Intel, sowie auf die RISC-Architektur PowerPC 604e [9] der Firma IBM abgebildet. Die Prozessoren dieser Hersteller werden deshalb als Beispiel herangezogen, da die Referenzhandbücher sich als detaillierte Beschreibung der Architekturen herausstellten.

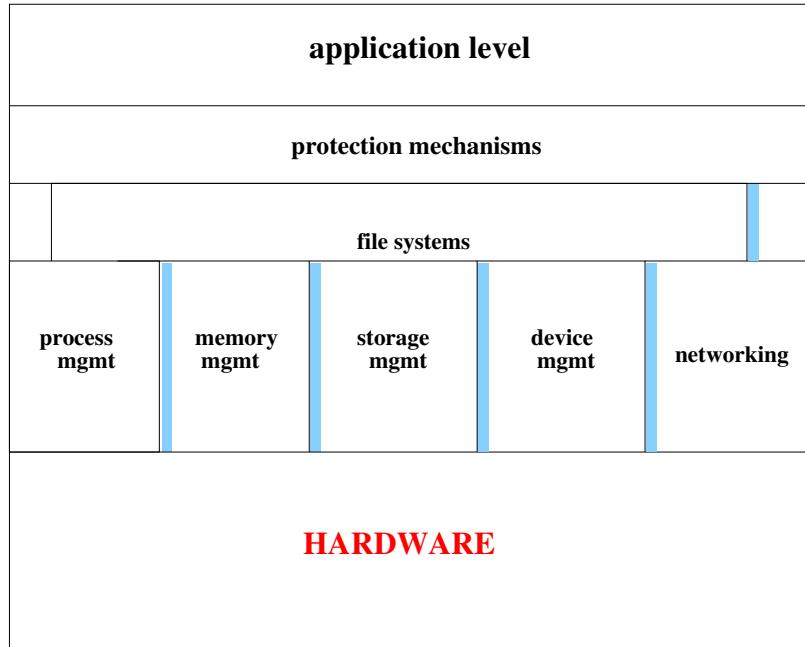

Den Abstraktionsstufen von der physikalischen Maschine aus nach oben folgend, steht das Betriebssystem im Weiteren im Mittelpunkt. Auch hier soll eine Aufstellung und anschließende Klassifizierung der relevanten Ereignistypen erfolgen, die ein Betriebssystem zur Verfügung stellen sollte. Untersucht wird am allgemeinen Aufbau eines Betriebssystems Prozess- und Thread-Management, die Speicherverwaltung, die Ein-/Ausgabe-Verwaltung, das Dateisystem und das Netzwerksubsystem [20]. Die Implementierung des gefundenen Klassenmodells wird an den Betriebssystemen Windows 2000 der Firma Microsoft und Linux aufgezeigt. Das Augenmerk soll auch hierbei auf die Kombinationsmöglichkeiten der einzelnen Klassen und deren Ereignistypen fallen, derart daß ein neuer Ereignistyp aus der Synthese zweier oder mehrerer verschiedener Ereignistypen entsteht und dem Anwender mehr Information liefern kann.

Damit der Anwender die Kombination von Ereignistypen nicht als eigenständige, fest

programmierte Algorithmen in Softwaremodulen umsetzen muß, wird eine allgemeine Spezifikationssprache vorgeschlagen. Die Definition eines Ereignistyps, sowie die Kombination dieser Typen soll so vereinfacht werden.

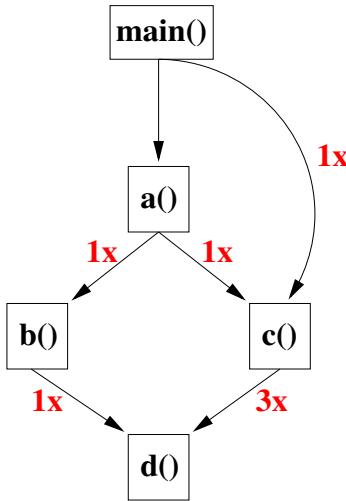

Liegen von einem Programm verschiedene Messungen vor, so ist es möglich, durch die Kombination der verschiedenen Daten das Ablaufprofil eines Programms zu vervollständigen. Dieser Aufgabe widmet sich der praktische Teil der Arbeit. Die Aufgabe besteht darin, die Gesamtheit der Kosten, die ein Programm während der Ausführung verursachte, auf die einzelnen Prozeduren im Programm zu verteilen. Kosten bezeichnen hier zum Beispiel die verbrauchten Zyklen, die Anzahl abgeschlossener Instruktionen, aber auch die Anzahl der erfolglosen Zugriffe auf die Cache–Hierarchie. Von einem Beispielprogramm ist nun einerseits das Ergebnis einer Simulation vorhanden, andererseits die Daten einer Sampling–Messung. Mit Simulationsdaten ist es möglich, den Kostenverbrauch exakt auf die Prozeduren zu verteilen. Sowohl die Kosten, die eine Prozedur selbst ohne ihre Aufrufe anderer Prozeduren verursacht<sup>1</sup>, als auch die akkumulierten Kosten, die zusätzlich entstehen, wenn eine Prozedur wiederum andere aufruft<sup>2</sup>, können in einer Simulation gemessen werden. Mit den Daten einer Sampling–Messung ist dies nicht möglich – allein die Selbstkosten können gemessen werden. Durch die Kombination der Information aus beiden Messungen, kann jedoch auf die Inklusivkosten geschlossen und damit die Sampling–Messung vervollständigt werden. Die von Profiling–Tools, wie `gprof` verwendete Heuristik [2] soll eine Verbesserung derart erfahren, daß die Verteilung der Kosten auf Prozeduraufrufe für bestimmte Situationen exakter wird und der genauen Berechnung, wie es in Simulationen möglich ist, näher kommt. Die gefundene Heuristik wird als Modul für ein Visualisierungsprogramm implementiert. Ein Gütemaß soll dann die Qualität der Heuristik bestätigen.

### 1.2 Relevante Arbeiten

Die grundlegenden Definitionen, sowie die Implementierung von Ereignissen und deren Erfassung in modernen Prozessoren finden sich in den Referenzhandbüchern der jeweiligen Hersteller [3, 6, 5, 9]. Diese Arbeiten erklären die unterschiedlichen Methoden der Zählung von Ereignissen, wie PEBS und Time–Based–Event–Counting. Es werden auch Verfahren angegeben, wie zum Beispiel das Auftreten von Ereignissen auf Quellcodeadressen abzubilden ist. Die Dokumentation der Bibliothek PAPI [8] erklärte die Kombination verschiedener Ereignistypen bei den betrachteten Prozessoren an den Stellen, an denen diese Kombinationen nicht in den technischen Unterlagen der Hersteller zu finden waren. Die Komponenten moderner Prozessorarchitekturen, wie zum Beispiel der TLB und die ALAT werden in den Arbeiten [13, 27, 38] vorgestellt und erklärt. Die Erkenntnisse aus diesen Arbeiten sind in die Klassifizierung eingeflossen. Bei der Klassifizierung von Ereignistypen der Peripherie gaben die technischen Handbücher und Arbeiten [22, 31, 23, 30, 28, 18] Hinweise ob vorgeschlagene Ereignistypen von Nutzen sind und ob diese bei den verschiedenen Herstellern der Peripheriegeräte umgesetzt wurden. Performance–Verluste durch sinkenden ILP behandelt die Arbeit von Gabbay und Mendelson [21]. Der Artikel von Choi [16] untersucht adaptive Mechanismen zur Lastverteilung auf verteilten Server–Cluster Systemen. In diesem Artikel

---

<sup>1</sup>Dies sind die Selbst– oder Exklusivkosten.

<sup>2</sup>Dies sind die Inklusivkosten.

werden die dafür nötigen Performance-Zähler angegeben. Die dort aufgeführten Ereignistypen und die Kombination dieser wurde in die Klassifizierung aufgenommen.

Auf der Seite der Software halfen die technischen Unterlagen [14, 17, 29, 7] der Betriebssysteme Windows 2000 und Linux bei der Erstellung der Klassifizierung. Aus [20] wurde die grundlegende Klassenhierarchie für die Ereignistypklassen der Software abgelesen.

Die Entwicklung der Spezifikationssprache wurde inspiriert von den Arbeiten [39, 15]. Die dort verwendeten Verfahren und Vorgehensweisen halfen bei der Spezifikation der Sprache.

### 1.3 Aufbau der Arbeit

Den vorangegangenen Überlegungen folgend, ergibt sich der Aufbau der Arbeit. Das Kapitel 2 ist den Definitionen der Begriffe Ereignis und Ereignistyp gewidmet. Es werden die verschiedenen Verfahren des Profilings erklärt und in Zusammenhang gebracht. Dieses Kapitel stellt die Basis für das folgende Kapitel 3 dar. In Kapitel 3 wird die Klassifizierung der Ereignistypen eines Rechensystems vorgeschlagen. Dazu beginnen die Abschnitte 3.1.1, 3.1.2 und 3.1.3 mit der Klassifizierung von Hardwareereignistypen für Prozessor, prozessorexternen Speicher und übrige Peripherie. Der Abschnitt 3.2 wendet sich dann der Software und der Klassifizierung von Ereignistypen in einem Betriebssystem zu. In den Abschnitten 3.2.1 bis 3.2.4 werden die Ereignistypen der Komponenten eines Betriebssystems einzeln beleuchtet und klassifiziert. Nachdem die Klassifizierung erfolgt ist, wird in Kapitel 4 auf die tatsächliche Umsetzung in Hard- und Software eingegangen. Das Kapitel spricht die Ereigniszähler der Prozessoren, der Peripherie und der Software an und stellt die Besonderheiten und Unterschiede der verschiedenen Systeme vor. Die Ereignistypklassen und ihre einzelnen Mitglieder werden nochmals aufgegriffen und untersucht, in wie fern sich diese bei den unterschiedlichen Produkten finden lassen.

Das Kapitel 5 beschäftigt sich mit der Entwicklung einer Spezifikationssprache, die es dem Anwender erleichtern soll, Ereignistypen und deren Kombination auf abstrakte Weise spezifizieren zu können. Dieses Kapitel stellt zunächst in Abschnitt 5.1.1 den Begriff Ereignistyp als Menge dar. In Abschnitt 5.2 wird die Grammatik der Spezifikationssprache angegeben und mit Hilfe der Mengendarstellung von Ereignistypen erläutert. Der letzte Abschnitt des Kapitels gibt einige einfache Beispiele in der Sprache an.

Den praktischen Teil dieser Arbeit fasst das Kapitel 6 zusammen. Es wird die Heuristik von gprof für die Berechnung von Inklusivkosten und die gefundene Quotientenheuristik erklärt. Die Ergebnisse dieser Messungen, einer Simulation und der realen Daten werden miteinander verglichen.

## 2 Performance–Messung – Grundbegriffe und Abgrenzung

Dieses Kapitel befasst sich mit der Klassifizierung von Ereignistypen der Hard- und Software. Bevor diese Einteilung vorgeschlagen wird, müssen die notwendigen Grundbegriffe vorgestellt und erklärt werden.

Moderne Hardwarearchitekturen enthalten Mechanismen, die es Profiling–Werkzeugen aktiv und direkt gestatten, geschwindigkeitskritische Komponenten zu beobachten. Darunter fallen unter anderem BPUs, Caches und Einheiten für die Übersetzung von virtuellen Speicheradressen. Die diesbezügliche Analyse von Anwendungen und Betriebssystemen ist wichtig für Compileroptimierungsstrategien und die effiziente Nutzung verschiedener architekturabhängiger Merkmale, wie der spekulativen Ausführung (vergleiche [5]).

### 2.1 Der Ereignistyp und das Ereignis

Wie schon in der Einleitung angesprochen, quantifizieren Ereignisse in einer Rechenanlage Vorgänge, die im Verlauf des Betriebs auftreten. Der Ereignistyp beschreibt die Bedingungen für das Auftreten und die gemessenen Attribute, die mit dem Auftreten eines Ereignisses eines Typs verbunden sind. Das Ereignis ist also quasi die Instanz eines Ereignistyps. Die Attribute eines Ereignisses sind zum Beispiel die Quellcodeadresse beim Auftreten, oder die Prozeß-ID des Prozesses, in dem das Ereignis auftrat. Während der Ausführungszeit eines Programms ändert sich der Zustand der Maschine. Wichtige Zustandsänderungen können klassifiziert und den Funktionseinheiten des Prozessors, respektive den Subsystemen des Betriebssystems zugeschrieben werden. Ein Performance–Zähler summiert das Auftreten von Ereignissen über einen bestimmten Zeitraum hinweg. Diese Zähler können durch Software gelesen und im Anschluß daran bildlich dargestellt werden.

#### 2.1.1 Ereignisarten

Es ist wichtig zu unterscheiden, wie oft ein Ereignis pro Zeiteinheit auftreten kann. Die folgende Aufzählung gibt einen Überblick:

- **Einzelereignisse (Single–Occurrence–Events):** Der betreffende Ereigniszähler wird um höchstens 1 pro Taktzyklus erhöht. Das heißt, pro Takt kann das Ereignis einmal oder nicht auftreten, nicht aber mehrmals. Beispiele für solche Ereignisse sind bezüglich der Hardware TLB–Misses oder falsch vorhergesagte Verzweigungen.

- **Duration–Counts:** Verwandt mit den Einzelereignissen sind die so genannten Duration–Counts. Hierbei wird ein Zähler pro Taktzyklus solange erhöht, wie eine bestimmte Bedingung erfüllt ist, ein Ereignis andauert. Nach [5] wird diese Zählweise zu den Einzelereignissen gezählt. Die Methode kommt zum Beispiel bei der Messung von Pipeline–Stalls zur Anwendung, wenn bestimmt werden soll, wie lange eine Pipeline angehalten werden mußte.

- **multiple Ereignisse (Multi–Occurrence–Events):** Ereignisse, die aufgrund des Hardware–Parallelismus oder der parallelen Ablaufströmen eines Programms entstehen, werden Multi–Occurrence–Events genannt. Pro Taktzyklus der Hardware kann ein Ereignis mehr als einmal auftreten. Beispiele für solche Ereignisse finden sich bei [6]. Dort wird unter anderem das Ereignis, welches die abgeschlossenen Instruktionen zählt genannt.

- **Thresholding:** Um beispielsweise die Frage, über wie viele Taktzyklen hinweg mehr als eine bestimmte Anzahl von Instruktionen abgeschlossen wurden, zu beantworten, kann ein Schwellwert gesetzt werden. Dieser bestimmt die Erhöhung eines Zählers derart, daß der betreffende Zähler nur dann erhöht wird, wenn der Schwellenwert überschritten ist. Thresholding und Duration–Counts bezeichnen dasselbe – Duration–Counts jedoch für die Einzelereignisse und Thresholding für Ereignisse die mehrfach pro Taktzyklus auftreten können.

## 2.2 Ereignisraten

Wenn die Performance eines Rechensystems untersucht wird, ist man nicht nur an der Häufigkeit des Auftretens eines Ereignisses zu einem bestimmten Zeitpunkt interessiert, sondern auch an der zeitlichen Veränderung des Vorkommens. Ereignisraten ermöglichen es, die Werte der Ereigniszähler über die Zeit der Ausführung eines Programms darzustellen. Zwei fundamentale Maße sind von Interesse: Ereignisraten (Event–Rate–Monitoring) und die Aufteilung von Programm–Zyklen zu den Ereignissen (Cycle–Accounting).

- **Event–Rate–Monitoring:** Wichtige Ereignisraten während der gesamten Laufzeit eines Programms umfassen beispielsweise die durchschnittliche Anzahl der ausgeführten Instruktionen pro Taktzyklus, die Rate der erfolglosen Zugriffe auf Daten– und Instruktion–Caches oder die Rate der falsch vorhergesagten Verzweigungen. Auch verlangt die Charakterisierung von Betriebssystemen oder großen kommerziellen Anwendungen (z.B. OLTP–Analyse) eine systemweite Sicht auf relevante Ereignisse wie TLB–Miss–Raten, Anzahl der Interrupts pro Sekunde oder die Busauslastung. Der Abschnitt 2.2.1 beschäftigt sich mit diesem Thema.

- **Cycle–Accounting:** Jeder Zyklus, den ein Programm während seiner Laufzeit verbraucht, kann bestimmten Ereignissen zugeschrieben werden. Nebst der dem Programm inhärenten Wartezeiten, werden zusätzlich Zyklen verbraucht die von Pipeline–Stalls oder Ähnlichem kommen. In Abschnitt 2.2.2 wird dieses Thema besprochen.

### 2.2.1 Event–Rate–Monitoring

Das Event–Rate–Monitoring bestimmt Ereignisraten durch das Lesen von Ereigniszählern vor und nach der Bearbeitung einer Arbeitslast, geteilt durch die verstrichene Zeit. Man stelle sich beispielsweise zwei Hardwarezähler vor. Der eine (`INST_RETIRED`) zähle die Anzahl der ausgeführten Instruktionen und der andere (`CPU_CYCLES`) die Zahl der verstrichenen Zyklen. Der IPC einer gegebenen Arbeitslast kann dann wie folgt berechnet werden:

$$IPC = \frac{(INST\_RETIRED_{t1} - INST\_RETIRED_{t0})}{(CPU\_CYCLES_{t1} - CPU\_CYCLES_{t0})}$$

### 2.2.2 Cycle–Accounting

Das Beobachten von Ereignisraten beschränkt sich im Wesentlichen auf das Zählen von Ereignissen mit Rücksicht auf die verstrichene Zeit. Ist ein Performance–Problem vorhanden, so ist aber nicht geklärt, inwiefern die beobachteten Ereignisse dazu beitragen. Üblicherweise werden dann die Raten der verschiedenen beobachteten Ereignisse graphisch dargestellt und in Zusammenhang mit dem IPC gesetzt. Stellt sich beispielsweise heraus, daß eine niedrige Rate abgeschlossener Instruktionen mit einem Anstieg erfolgloser Cache–Zugriffe korreliert, kann die Hypothese aufgestellt werden, daß die Cache–Zugriffe ursächlich für das Problem sind. Solche Vermutungen sind nur mit viel Erfahrung aufzustellen und zu verifizieren. Manche Hardwarearchitekturen unterstützen die Programmierer hierbei in der Weise, daß für einige Ereignisse Cycle–Accounting–Monitore bereitgestellt werden. Es besteht so die Möglichkeit jeden Taktzyklus eines Programms einem bestimmten Typ von Ereignis zuzuordnen. Da die meisten Taktzyklen durch Stall– oder Flush–Bedingungen verschiedener Pipelines verbraucht werden und dieser Verbrauch nur schwer den Verursachern zuordnen ist, liegt das Augenmerk der Unterstützung auf den Stalls/Flushes der Pipelines, unter Anderem für:

- Branch Prediction

- Memory Pipelines, Daten–TLB– und andere Load–Stalls

- Scoreboard– und FPU–Stalls

- Instruction–Issue–Stops<sup>1</sup>

- Instruction–Fetch–Stalls<sup>2</sup> auf Grund von Instruction–Cache– oder TLB–Misses

Die Implementierung des Cycle–Accounting wird für die untersuchten Architekturen in Kapitel 4 angesprochen. Es ist zu beachten, daß Cycle–Accounting–Mechanismen sich vom Duration–Counting der Stalls und Flushes unterscheiden. Während beim Cycle–Accounting die verbrauchten Taktzyklen bestimmten Verursachern zugerechnet werden können, beschränkt sich das Duration–Counting auf die Gesamtheit der durch Stalls und Flushes verursachten Latenzzeiten.

<sup>1</sup>Situation, bei der die Verteilung von Instruktionen auf die Einheiten der CPU angehalten werden muß. Dies kann zum Beispiel bei Datenabhängigkeiten der Fall sein.

<sup>2</sup>Situation, wenn eine Instruktion nicht sofort verfügbar ist und Wartezyklen entstehen, weil die Instruktion von einem langsameren Speicher geladen werden muß.

## 2.3 Statistisches Sampling

Beim Sampling wird in bestimmten Abständen eine Messung vorgenommen. Je nach Modell sind die Abstände verschieden. In bestimmten Intervallen werden also Stichproben genommen und der Codezeile zugeordnet.

Beim Begriff statistisches Sampling kann wie folgt unterschieden werden:

- **Time–Based–Sampling:** Die Abstände, in denen Messungen vorgenommen werden, sind durch zeitliche Intervalle definiert. Diese Intervalle können einerseits fest sein andererseits einen variablen und eventuell zufälligen Anteil haben. In festen Zeitabständen die Messung vorzunehmen hat den Nachteil, daß bei Programmstrukturen wie Schleifen die Messung häufig an der selben Stelle im Code stattfindet. Damit die gemessenen Ereignisse nicht stets der selben Codezeile zugeordnet werden, kann das Intervall zufällig gewählt werden. Meist geschieht dies durch Vergrößerung, beziehungsweise Verkleinerung des Intervalls um eine zufällige Größe. Der Unterabschnitt 2.3.1 befasst sich mit diesem Thema.

- **Event–Based–Sampling:** Die Messungen werden nach einer definierten Anzahl aufgetretener Ereignisse vorgenommen. Eine zufällige Änderung des Schwellenwertes, ähnlich einem variablen Zeitintervall, ist ebenso vorstellbar und ermöglicht wiederum eine bessere Verteilung der Stichproben über den Code. In Unterabschnitt 2.3.2 wird auf dieses Thema eingegangen.

### 2.3.1 Time–Based–Sampling

Die Meßmethoden verfälschen das Ergebnis, da die Messung selbst Zeit in Anspruch nimmt. Um den Fehler so gering wie möglich zu halten, benutzen viele Performance–Analyse–Tools für die Messungen das so genannte Time–Based–Sampling (siehe [2, 24]). In regelmäßigen Zeitabständen (zum Beispiel 1ms) sammelt das Tool zum Beispiel die Instruktionsadressen. Die Verfälschung der Messung kann so beim Sampling durch die Wahl des Intervalls eingestellt werden. Nach Beendigung des Programmlaufs werden diese Daten den Modulen etc. zugeordnet, so daß ein Bild davon entsteht, welche Teile des Programms am meisten Zeit verbrauchen und welche Codeadressen am häufigsten angesprungen werden. Dem Programmierer zeigt eine graphische Darstellung, wo im Programm die so genannten Hot–Spots zu finden sind. Vorteil dieser Methode ist, daß die Daten nicht für jede ausgeführte Codezeile aufgezeichnet werden und somit die Anzahl der damit verbundenen (Fest–)–Speicherzugriffe deutlich vermindert und der Overhead, den die Sammlung von Stichproben mit sich bringt verringert wird. Das Verfahren wird durch die Annahme gerechtfertigt, daß sich die Verteilung der gemessenen Werte nur unwesentlich im Vergleich zu einer exakten Messung ändert.

### 2.3.2 Event–Based–Sampling

Eine andere Herangehensweise stellt das Event–Based–Sampling dar. Hier wird zum Beispiel die aktuelle Codeadresse aufgezeichnet, nachdem eine bestimmte Anzahl von

Prozessor– oder Softwareevents erreicht wurde. Gleichesmaßen wie in 2.3.1 ist nach Ablauf des Programms dieser Wert den Modulen zuzuordnen. Die modernen Prozessorarchitekturen unterstützen das Event–Based–Sampling bereits durch die Hardware. In Kapitel 4, Abschnitt 4.1.1.1 werden die konkreten Realisierungen angesprochen.

### 2.3.3 Präzises attributieren der Samples

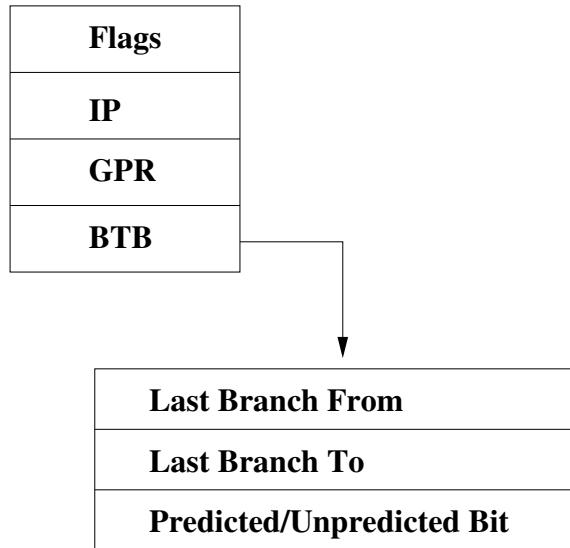

Die in den Abschnitten 2.3.1 und 2.3.2 genannten Verfahren haben zur Folge, daß nach bestimmten Zeitintervallen oder einer festgelegten Anzahl von Ereignissen detaillierte Daten über den Zustand der Maschine gesammelt werden können. Diese Vorgehensweise wird hier als präzises Sampling bezeichnet. Für die in Kapitel 3 angestrebte Klassifizierung muß daher eine Datenstruktur gefunden werden, die diese Informationen aufnimmt. Eine detaillierte Datensammlung verbraucht natürlicherweise Zeit, welche das Meßergebnis beeinflußt (vergleiche Abschnitt 2.3.1). Zur Unterscheidung von präzisem Sampling und einfaches Sampling spricht man Falle des Time–Based–Sampling vom Precise–Time–Based–Sampling (**PTBS**), im Falle des Event–Based–Sampling vom Precise–Event–Based–Sampling (**PEBS**). In Kapitel 4 werden die konkreten Möglichkeiten der Realisierung bei den verschiedenen Architekturen angesprochen. Ist dieser Detailgrad nicht vonnöten, so kann nur der Instruktionszeiger zusammen mit den gemessenen Ereignissen protokolliert werden. Folgende Punkte sind zu betrachten, wenn der Zustand des Rechners zum Zeitpunkt der Messung genau beschrieben werden soll, um eine Rückverfolgung in den Code zu ermöglichen:

- **Die Registerinhalte:** Die Registerinhalte sind für das präzise Sampling von geringerer Bedeutung. Für das Debuggen von Programmen bekommen die Registerinhalte mehr Bedeutung.

- **Die Statusflags:** Die Betrachtung des Prozessorstatusworts gibt Aufschluß über die Bedingungen von Vergleichen und Ähnlichem zum Zeitpunkt des Auftretens des Ereignisses.

- **Der Instruktionszeiger:** Die Adresse, die der Instruktionszeiger enthält, macht die Rückverfolgung in den Quellcode erst möglich.

- **Der Branch–Trace–Buffer:** Im Branch–Trace–Buffer steht die Adresse der Instruktion von der aus die letzte Verzweigung ausging, sowie die Adresse der ersten Instruktion des Verzweigungsziels. Außerdem enthält der Puffer noch ein Bit, welches anzeigt ob diese Verzweigung korrekt vorhergesagt wurde. Die Analyse dieser Struktur zeigt welche Sprünge im Programm durch falsche Vorhersage Performance–Probleme verursachen, so daß Lösungen gezielt gesucht werden können.

Ein Record–Eintrag der Datenstruktur ist in Abbildung 2.1 dargestellt:

Diese Punkte stellen die gemeinsamen Attribute aller Ereignistypen dar. Für bestimmte Klassen von Ereignistypen werden in Kapitel 3 zusätzliche Attribute vorgeschlagen.

Abbildung 2.1: Die Recordstruktur für präzises Sampling.

## 2.4 Codeinstrumentierung

Bei der Codeinstrumentierung wird zusätzlicher Code in den Quelltext eines Programms eingefügt. Solche zusätzlichen Codeteile protokollieren während der Ausführung des Programms zum Beispiel die Anzahl der Funktionsaufrufe, welche Funktion von welcher Stelle aufgerufen wurde, oder wie viel Zeit in den einzelnen Programmabschnitten verbraucht wurde. Der Nachteil besteht im Gegensatz zum statistischen Sampling darin, daß der Quelltext des zu untersuchenden Programms verändert werden muß. Auch verfälscht die Instrumentierung das Ergebnis der Analyse, da der Code der Instrumentierung ebenfalls ausgeführt wird. Der Vorteil liegt in der Tatsache, daß durch die exakte Messung ein exaktes Profil des Programms erstellt werden kann. Die Messung der Inklusiv-/Exklusivkosten von Funktionen (vergleiche Kapitel 6) stellt mit Codeinstrumentierung kein Problem dar. Die Instrumentierung von Programmen kann auf den unterschiedlichen Ebenen der Quelltexttransformation stattfinden. Es existieren Programme, die den Code zur Laufzeit verändern, aber auch das manuelle Hinzufügen auf Hochsprachenebene ist möglich. Ein Beispiel für die Instrumentierung zur Laufzeit ist PureCoverage der Firma Rational [19] für die Instrumentierung von Java–Code.

## 2.5 Profiling

Das Thema des Profiling befasst sich mit der Sammlung von Daten über den Ablauf eines Programms. Für den Anwender steht dabei die Rückverfolgbarkeit in den Quellcode im Vordergrund. Das Profiling verwendet die oben vorgestellten Verfahren und erstellt ein Profil der laufenden Anwendung, um unter Anderem Antworten auf folgende Fragen (vergleiche [36]) zu finden:

- Wie viel Zeit nahm die Ausführung einer Funktion in Anspruch?

- Wie oft wurde eine bestimmte Funktion aufgerufen?

- Welche Zeilen des Sourcecodes benötigten die meiste Zeit zur Ausführung?

Diese Informationen zeigen, welche Programmteile langsamer ablaufen als erwartet und wo Veränderungen und Optimierungen am ehesten Erfolg versprechen. Profiling–Tools wie `gprof` [2] unterscheiden üblicherweise zwischen drei Ausgaben, deren Informationsgehalt verschieden ist. In [2] sind die verfügbaren Ergebnisse eines Profiling–Laufs wie folgt beschrieben:

- **Flat Profile:** Das Flat Profile zeigt, wie viel Zeit in jeder Funktion verbraucht und wie oft diese Funktion aufgerufen wurde. Mit dieser Information ist ersichtlich, welche Funktion die meisten Taktzyklen benötigte. So genannte Hot–Spots im Code, die Häufung der Ausführung bestimmter Codeabschnitte, sind auf diese Weise erkennbar.

- **Call Graph:** Der Aufrufbaum zeigt die Aufrufabhängigkeiten der verschiedenen Funktionen und zeigt an, wie viel Zeit in den Subroutinen einer jeden Funktion verbraucht wurde. Für den Programmierer eröffnet sich daher die Möglichkeit eventuell unnötige Funktionsaufrufe zu erkennen und zu eliminieren. Angaben über die Zeit die eine Funktion und ihre Subroutinen verbraucht stellen allerdings ein Problem dar, auf das in Kapitel 6 eingegangen wird.

- **annotierter Sourcecode:** Die Ausgabe des annotierten Sourcecodes fügt dem Programm in jeder Zeile eine Angabe bei, die darüber Auskunft gibt, wie oft diese Zeile ausgeführt wurde.

Wenn die gesammelten Daten als Eingabe für so genannte Profile–Guided Compiler benutzt werden können, so ist es möglich, automatische Korrekturen durch den Übersetzer und Linker in den Übersetzungsprozeß einfließen zu lassen. Essentiell für das Profiling ist die angesprochene Zurückverfolgbarkeit der gemessenen Ereignisse in den Sourcecode. Ist nicht nur die Häufigkeit des Aufrufs einzelner Codezeilen und Funktionen von Interesse, sondern auch der Grund für gewisse Performance–Probleme, dann ist es wünschenswert, wenn die Hardware den Anwender durch Zählerregister für Ereignistypen unterstützt.

## 2.6 Simulation

Ein weiteres Verfahren, Daten über den Ablauf eines Programms zu erhalten, stellt die Simulation dar. Bei der Simulation wird das zu untersuchende Programm auf dem Modell einer Hardwarearchitektur ausgeführt. Die Software des Simulators imitiert also einen Prozessor. Es liegt der Vorteil des Verfahrens darin, daß die Messung von Ereignissen nicht mehr an die Ereignistypen und Ereigniszähler des Prozessors gebunden ist, sondern die Simulation diese Typen und deren Messung zur Verfügung stellt. So ist es beispielsweise möglich, Ereignisse, wie Prozedureinsprünge und Prozedurrücksprünge zu messen, die allein mit den Möglichkeiten der Hardware nicht zur Verfügung stehen. Der Nachteil liegt zum einen in der Tatsache begründet, daß die Simulation durch ihre eigene Ausführung Overhead erzeugt,

welcher in das Ergebnis einfließt und dieses verfälscht. Andererseits hängen die Ergebnisse auch davon ab, in wie weit die Simulation die imitierte Hardware annähert. Weicht das Verhalten der simulierten Hardware stark von dem der konkreten Architektur ab, so sind die Ergebnisse nicht mehr aussagekräftig.

Der Open–Source Cache–Simulator Valgrind [32] ist ein Beispiel für dieses Verfahren. Das Programm simuliert eine CPU, auf der das zu analysierende Programm ausgeführt wird. Die simulierte CPU stellt dabei Ereignistypen für die Erstellung von Cache– und Heap–Profilen und die Erkennung von Speicher– und Thread–Fehlern zur Verfügung. Auf einer konkreten Maschine ist dies dagegen nicht, oder nur eingeschränkt möglich.

# 3 Die Klassifizierung von Ereignistypen

Nachdem die Grundbegriffe der Ereignistypen in Kapitel 2 geklärt worden sind, kann die Einteilung der Ereignistypen in Klassen erfolgen. Zunächst gehen die Abschnitte 3.1 – 3.2 von einer theoretischen Betrachtung aus, das heißt, daß die Klassifizierung der Ereignistypen ohne Rücksicht auf die tatsächliche Umsetzung der Hersteller von Prozessoren und Betriebssystemen betrachtet wird. Dahinter steht der Zweck, einen Gesamtüberblick über die Möglichkeiten und den Nutzen verschiedener Ereignistypen zu geben. Die in diesem Abschnitt vorgeschlagene Einteilung gruppiert die Vielzahl von Ereignistypen und stellt deren Zusammenhänge dar. Für einen besseren Überblick bedienen sich die Abschnitte der UML-Notation [12].

## 3.1 Hardware

Bei der Klassifizierung der in der Hardware auftretenden Ereignisse, ist es sinnvoll sich am prinzipiellen Aufbau einer Rechenanlage zu orientieren, um so die Überklassen zu identifizieren. Grundsätzlich besteht ein Rechner aus dem Prozessor, an den die Peripherie angeschlossen wird. Zunächst sei das Augenmerk auf den Prozessor gelegt, danach wird die Peripherie betrachtet. Bei den schematischen Darstellungen wird zwar auf die jeweilige Architektur hingewiesen, diese jedoch öfters gemischt. Auf der hier betrachteten Ebene spielen die Unterschiede zwischen RISC- und CISC-Systemen keine Rolle, da eine für die Architekturen gleichförmige Klassifizierung gefunden werden soll.

### 3.1.1 Prozessor

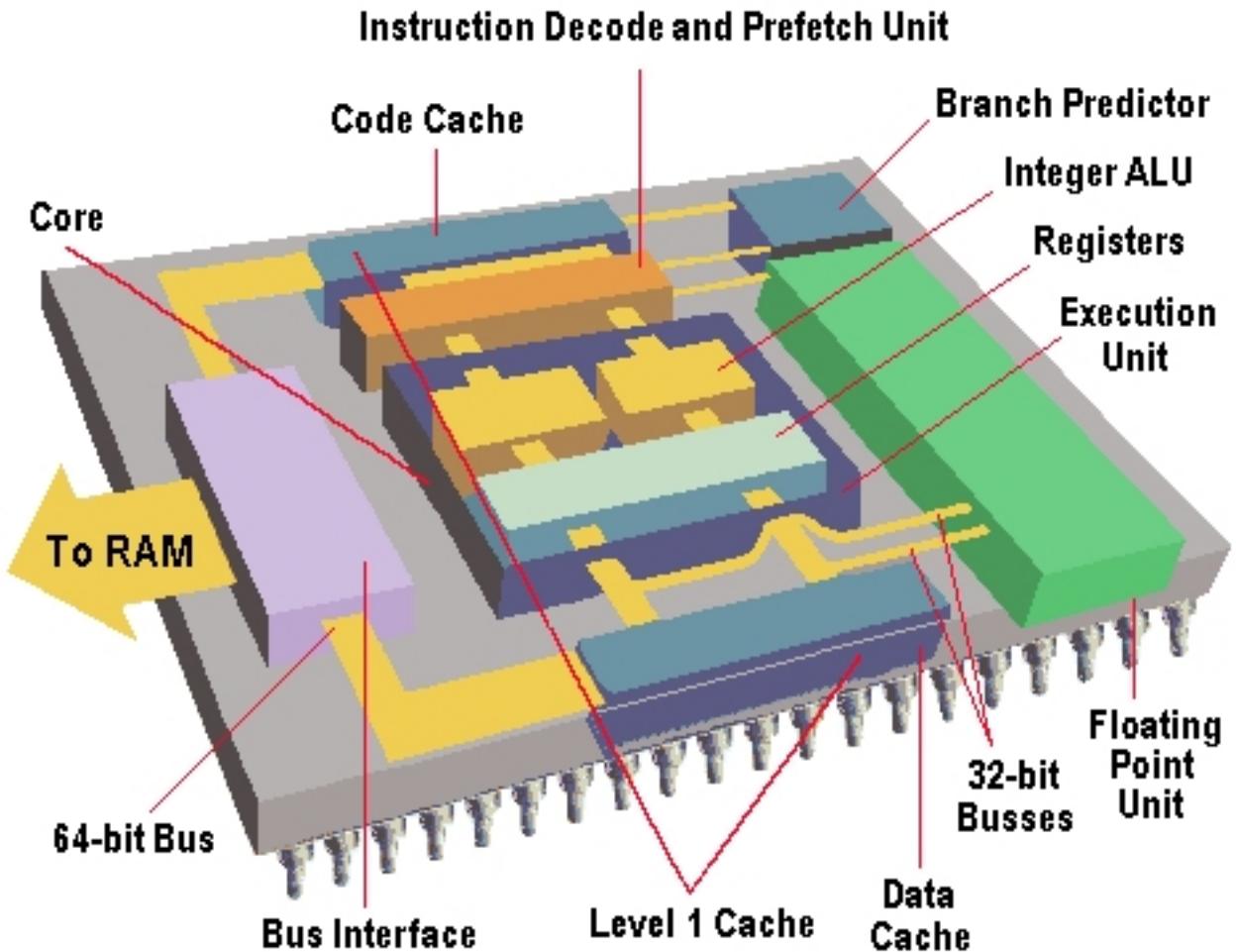

Dieser Abschnitt befasst sich mit der zentralen Einheit, der CPU, einer Rechenanlage. Aus der schematischen Darstellung eines Prozessors soll die Ereignistypklassifizierung abgelesen werden. In Abbildung 3.1 ist ein solcher Aufbau schematisch dargestellt. Es handelt sich hier um die Darstellung eines Pentium-Prozessors der Firma Intel, also eine CISC-basierte Architektur. Die gezeigten funktionalen Einheiten sind jedoch auch in den RISC-Systemen anderer Hersteller vorhanden und unterscheiden sich lediglich in der Implementierung.

Aus der Abbildung können die nachfolgenden fünf Klassen abgelesen werden. Sie bilden übergeordnete Einheiten und daher liegt es nahe die Modellierung in UML als Interface vorzunehmen. Von jedem Interface werden im Verlaufe des Kapitels Klassen abgeleitet, welche die einzelnen Ereignistypen aufnehmen.

- **Branch Predictor:** Die BPU ist für alle Aufgaben zuständig, die mit der Ausführung von bedingten und unbedingten Sprüngen zusammenhängen. Insbesondere wird in dieser Einheit bei den modernen Prozessoren die Sprungzielvorhersage berechnet. Die

Abbildung 3.1: Schematischer Aufbau eines Prozessors – IA-32 Pentium der Firma Intel.

dazugehörigen Ereignistypen werden durch das Interface `BRANCH_EVENTS` zusammengefasst.

- **Level 1 Cache, Level 2 Cache, Level 3 Cache:** Je nach Hersteller findet sich eine mehr oder weniger stark ausgeprägte Cache-Hierarchie im Prozessor. Meist ist der Level 1 Cache ein so genannter Split-Cache bei dem Daten und Instruktionen getrennt von einander in verschiedenen Speicherbereichen abgelegt werden. Die Performance eines Programms wird sehr durch die Rate der erfolgreichen Zugriffe auf diese Cache-Hierarchie bestimmt. Alle Ereignistypen die sich mit den Caches zusammenhängen werden mit dem Interface `MEMORY_HIERARCHY` zusammengefasst.

- **Instruction-Decode und Instruction-Prefetch:** Dieser Teil des Prozessors dekodiert Instruktionen, ist aber auch dafür verantwortlich Instruktionen im Voraus zu laden. Das Interface `BASIC_EVENTS` wird Ereignistypen wie zum Beispiel die Anzahl der abgeschlossenen Instruktionen etc. beschreiben.

- **Integer ALU und FPU:** Die Execution-Unit enthält in der Abbildung die Integer-ALU

und die Register. Die dekodierten Instruktionen werden hier verarbeitet. Die FPU gehört zu den die Instruktionen ausführenden Einheiten, so daß auch diesen Teil des Prozessors betreffende Ereignistypen unter dem Interface `INSTRUCTION_EXECUTION` zusammengefasst werden können.

- **Bus Interface:** Die Auslastung der Busse kann Auswirkungen auf die Performance haben, so daß auch hier Ereignistypen und Ereignisraten wichtige Informationen geben können. Das Interface `SYSTEM_EVENTS` enthält aber auch Ereignistypklassen, die unter Anderem die Anzahl der System-Calls, der Interrupts oder der Zugriffe auf den Bus beschreiben.

In 2.2.2 wurde angesprochen, daß es von Vorteil ist, zu wissen wie sich die verbrauchten Zyklen einer Programmausführung auf die Prozessoreinheiten aufteilen. Dem folgend fasst das Interface `CYCLE_ACCOUNTING` Ereignistypen zusammen, die beispielsweise Auskunft geben über die Anzahl der Zyklen während derer die FPU keine Instruktionen verarbeiten konnte.

In den folgenden Abschnitten werden Klassen von den Interfaces abgeleitet. Diese Klassen enthalten die Ereignistypen.

Zur Notation sei gesagt, daß direkt meßbare Ereignisse bestimmter Ereignistypen in Maschinenschrift und Großbuchstaben gekennzeichnet sind (`EREIGNISTYP`). Von diesen Ereignistypen, durch Kombination verschiedener anderer Ereignistypen, abgeleitete Typen werden zusätzlich mit `.d` gekennzeichnet.

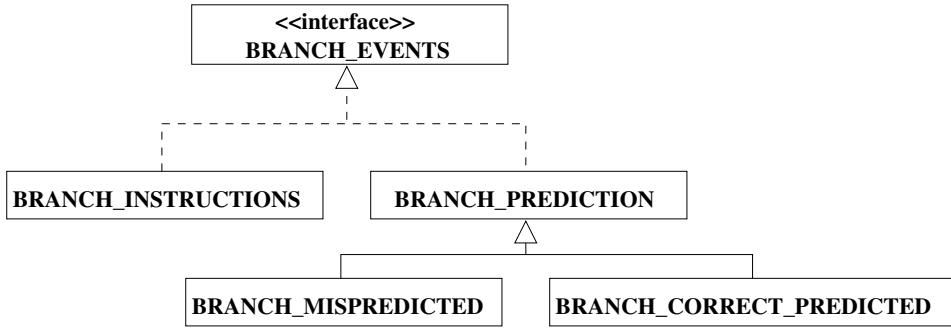

#### 3.1.1.1 Das Interface `BRANCH_EVENTS`

Unter dem Interface `BRANCH_EVENTS` werden Ereignistypen zusammengefasst, die eine möglichst genaue Untersuchung der Sprungzielvorhersage ermöglichen sollen. Die Ereignistypen werden in zwei Kategorien aufgeteilt:

1. **BRANCH\_INSTRUCTIONS:** Die Attribute dieser Klasse modellieren Ereignistypen, die generell die dekodierten und abgeschlossenen Sprungbefehle beschreiben.

2. **BRANCH\_PREDICTION:** Mit dieser Klasse soll die Sprungzielvorhersage erfasst werden. Um eine genaue Analyse zu ermöglichen, werden Ereignistypen modelliert, die separat die zwei unterschiedlichen Richtungen einer Verzweigung und den Ausgang der Vorhersage beschreiben.

Die Abbildung 3.2 zeigt die Hierarchie der im folgenden beschriebenen Klassen.

#### 3.1.1.2 Die Klasse `BRANCH_INSTRUCTIONS`

Die Ereignistypen dieser Klasse umfassen die dekodierten und die abgeschlossenen Branch-Instruktionen. Durch Instruction-Prefetching ist es möglich, daß mehr Instruktionen dekodiert als abgeschlossen wurden. Unter Umständen ist ein solcher Zustand ein Hinweis für

Abbildung 3.2: Die Klassenhierarchie unter dem Interface `BRANCH_EVENTS`.

Pipeline-Stalls oder eine nicht erfolgreiche Sprungzielvorhersage. Das Verhalten eines Programms kann noch genauer untersucht werden, wenn es möglich ist, auch die unbedingten Sprünge zu zählen. Profiling-Tools sind dann in der Lage Prozedureinsprünge besser zuordnen und so den Zeitverbrauch in den Prozeduren bestimmen zu können (siehe Kapitel 6). Sinnvolle Attribute der Ereignistypen dieser Klasse sind diejenigen aus Abschnitt 2.3.3. Vor allem der Branch-Trace-Buffer enthält bei unbedingten Sprüngen Informationen zu Prozedureinsprung und Prozedurrücksprung. Folgende Ereignistypen sind in der Klasse enthalten:

1. **BRANCH\_INSTRUCTIONS\_DECODED**: Ereignisse dieses Typs zählen die Anzahl der dekodierten, aber nicht zwingend abgeschlossenen Instruktionen. Sowohl bedingte als auch unbedingte Sprünge werden gezählt.

2. **BRANCH\_INSTRUCTIONS\_RETIRIED**: Die abgeschlossenen Sprungbefehle werden mit Ereignisen dieses Typs gezählt.

3. **BRANCH\_INSTRUCTIONS\_UNCONDITIONAL\_RETIRIED**: Die abgeschlossenen unbedingten Sprungbefehle werden mit Ereignissen dieses Typs ermittelt.

Die Klasse modelliert zusätzlich die folgenden abgeleiteten Ereignistypen:

1. **BRANCH\_INSTRUCTIONS\_CONDITIONAL\_RETIRIED.d**: Die Ereignisse dieses Typs berechnen sich nach folgender Vorschrift:

$$\text{BRANCH\_INSTRUCTIONS\_RETIRIED} - \text{BRANCH\_INSTRUCTIONS\_UNCONDITIONAL\_RETIRIED}$$

Mit dem Ereignistyp wird die Anzahl der bedingten Sprunganweisungen beschrieben.

2. **BRANCH\_INSTRUCTIONS\_DECODED\_RETIRIED\_RATIO.d**: Das Verhältnis von dekodierten zu abgeschlossenen Sprungbefehlen wird wie folgt berechnet:

$$\frac{\text{BRANCH\_INSTRUCTIONS\_DECODED}}{\text{BRANCH\_INSTRUCTIONS\_RETIRIED}}$$

Das Verhältnis kann, wie oben erwähnt, auf ungünstiges Instruction-Prefetching oder Pipeline-Stalls hinweisen.

3. **BRANCH\_INSTRUCTIONS\_RETIRED\_PER\_CYCLE.d**: Die Anzahl der ausgeführten Sprungbefehle pro Taktzyklus geben Aufschluß über die Linearität des Programms und werden nach folgender Formel berechnet:

$$\frac{\text{BRANCH\_INSTRUCTIONS\_RETIRED}}{\text{CPU\_CYCLES}}$$

### 3.1.1.3 Die Klasse BRANCH\_PREDICTION

Ereignisse der Ereignistypen dieser Klasse treten bei den bedingten Verzweigungen auf. In der Klasse werden folgende Ereignistypen vorgeschlagen:

1. **BRANCH\_TAKEN**: Der Ereignistyp beschreibt die `taken`-Branches, die Verzweigungen die im `if`-Zweig enden.

2. **BRANCH\_NOT\_TAKEN**: Mit diesem Ereignistyp werden die so genannten `not-taken`-Branches, die `then`-Zweige beschrieben.

Die Klasse enthält des weiteren einen abgeleiteten Ereignistyp:

1. **BRANCH\_ALL.d**: Die bedingten Sprünge, unabhängig vom Ausgang der Verzweigung können wie folgt beschrieben werden:

$$\text{BRANCH\_TAKEN} + \text{BRANCH\_NOT\_TAKEN}$$

In dieser Klasse ist dieser Ereignistyp und der Ereignistyp **BRANCH\_INSTRUCTIONS\_CONDITIONAL\_RETIRED.d** aus Abschnitt 3.1.1.2 identisch.

### 3.1.1.4 Die Klasse BRANCH\_MISPREDICTED

Diese Klasse leitet direkt von der Klasse **BRANCH\_PREDICTION** ab. Sie übernimmt daher alle Ereignistypen und den abgeleiteten Typ **BRANCH\_ALL.d**. Diese Ereignistypen haben die selbe Bedeutung, sie beschränken sich aber auf Verzweigungen, die von der Branch-Prediction-Unit (vergleiche Abbildung 3.1) nicht korrekt vorhergesagt wurden. Zusätzlich enthält die Klasse zwei Ereignistypen, mit denen der Grund der falschen Vorhersage genauer analysiert werden kann:

1. **BRANCH\_MISPREDICTED\_WRONG\_PATH**: Die Branch-Prediction-Unit hat den falschen Pfad vorhergesagt. Der Ereignistyp beschreibt diese Art der falschen Vorhersage.

2. **BRANCH\_MISPREDICTED\_WRONG\_TARGET**: Wurde das Ziel des bedingten Sprunges falsch vorhergesagt, so treten Ereignisse dieses Typs auf.

### 3.1.1.5 Die Klasse BRANCH\_CORRECT\_PREDICTED

Ebenso wie die Klasse BRANCH\_MISPREDICTED leitet sich diese Klasse von BRANCH\_PREDICTION ab. Alle ererbten Ereignistypen beziehen sich hier auf die korrekte Vorhersage der Branch-Prediction-Unit. Weiter Ereignistypen sind in dieser Klasse nicht enthalten.

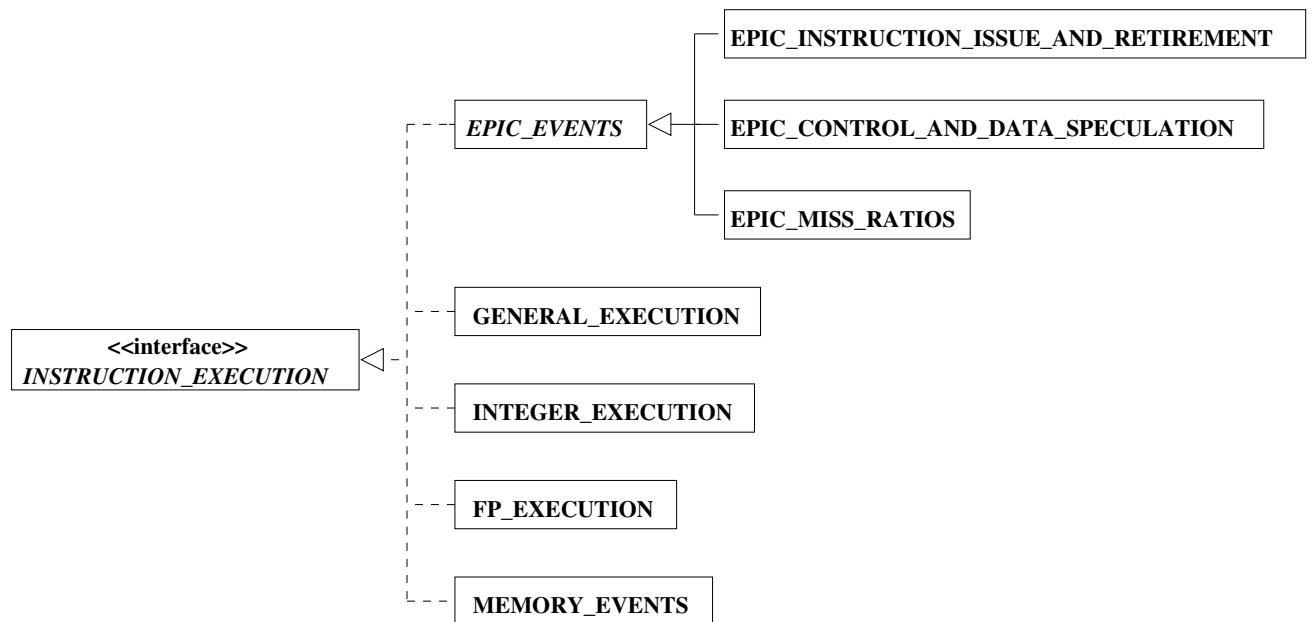

### 3.1.1.6 Das Interface INSTRUCTION\_EXECUTION

Unter dem Interface INSTRUCTION\_EXECUTION sind Ereignistypen zusammengefasst, die sich mit der Ausführung der Maschinenbefehle beschäftigen – diese gliedern sich in fünf Gruppen. Es wird im Hinblick auf Kapitel 4 auf eine allgemeine Beschreibung Wert gelegt. Da Intel einen Trend zu EPIC angestoßen hat, der Itanium im Moment zwar noch der einzige bekannt Vertreter ist, finden sich die zu Kontroll- und Datenspekulation gehörenden Ereignistypen in der abstrakten Klasse EPIC\_EVENTS. Die anderen vier Gruppen enthalten sowohl Ereignistypen der Floating-Point- und der Integer-Berechnung als auch Ereignisse das Laden und Speichern von Registern betreffend und der generellen Instruktionsausführung. In der Abbildung 3.3 ist die Klassenhierarchie dargestellt.

Abbildung 3.3: Die Klassenhierarchie unter dem Interface INSTRUCTION\_EXECUTION.

Im folgenden sind die Klassen beschrieben:

- **EPIC\_EVENTS**: Diese abstrakte Klasse bündelt die für EPIC-spezifischen Ereignistypen zur Kontroll- und Datenspekulation und gliedert sich daher in die Klassen EPIC\_INSTRUCTION\_ISSUE\_AND\_RETIREMENT, CONTROL\_AND\_DATA\_SPECULATION und EPIC\_MISS\_RATIOS auf.

- **FP\_EXECUTION:** Diese Klasse enthält Ereignistypen, die die Ausführung von Floating-Point-Instruktionen betrifft.

- **INTEGER\_EXECUTION:** In dieser Klasse befinden sich Ereignistypen der Integer-Einheit.

- **GENERAL\_EXECUTION:** Diese Klasse befasst sich mit der Instruktionsausführung im Allgemeinen.

- **MEMORY\_EVENTS:** Die Klasse enthält Ereignistypen, die das Laden und Speichern von Daten beschreiben.

#### 3.1.1.7 Die abstrakte Klasse EPIC\_EVENTS

EPIC-Architekturen spezialisieren VLIW-Architekturen und versuchen den ILP in jedem Programm zu verbessern. Die größten Hindernisse für einen Compiler dies zu erreichen, sind der häufige Kontrolltransfer und unklare Datenabhängigkeiten [13, 21]. EPIC-Architekturen unterstützen den Compiler durch Daten- und Kontrollspekulation. Folglich sind spezielle Datenstrukturen von Nöten. Von dieser abstrakten Basisklasse leiten sich die Klassen EPIC\_INSTRUCTION\_ISSUE\_AND\_RETIREMENT, EPIC\_CONTROL\_AND\_DATA\_SPECULATION und EPIC\_MISS RATIOS ab. In diesen Klassen finden sich Ereignistypen, die die Verfügbarkeit der funktionalen Einheiten und die spekulative Ausführung beschreiben. Da der Geschwindigkeitsgewinn eines Programms von der erfolgreichen Spekulation abhängt sind in der Klasse EPIC\_MISS RATIOS die Raten der fehlgeschlagenen Spekulationen modelliert.

#### 3.1.1.8 Die Klasse EPIC\_INSTRUCTION\_ISSUE\_AND\_RETIREMENT

Mit den Ereignistypen der Klasse werden folgende Ereignisse beschrieben:

- **INSTRUCTIONS\_DISPERSED:** Der Ereignistyp beschreibt die Anzahl der Instruktionen, die dem Kern zugeführt wurden und auf die funktionalen Einheiten verteilt (dispersed) werden.

- **EXPLICIT\_STOPS:** Das Ereignis dieses Typs tritt auf, wenn sich im abzuarbeitenden Instruktionsstrom eine explizite Stop-Anweisung befindet, so daß die parallele Ausführung von Anweisungen unterbrochen wird. Dies hat Auswirkung auf den ILP und somit auf die Performance des Programms [21].

- **IMPLICIT\_STOPS\_DISPERSED:** Sind einige Einheiten, etwa durch komplexe Berechnungen nicht verfügbar, so muß die ansonsten parallel ausführbare Menge von Instruktionen angehalten werden. Auch diese Unterbrechungen beeinflussen den ILP und können über Ereignisse dieses Typs identifiziert werden.

#### 3.1.1.9 Die Klasse EPIC\_CONTROL\_AND\_DATA\_SPECULATION

EPIC-Architekturen wie der Intel Itanium unterstützen das spekulative Laden von Daten auch über Kontrollstrukturen hinweg. Bevor die Ereignisse der Klasse EPIC\_CONTROL\_AND\_DATA\_SPECULATION behandelt werden können, muß das Verfahren des spekulativen und vorgezogenen Ladens erklärt werden [4].

Die folgende Terminologie bedarf der Unterscheidung und Erklärung:

- **Datenspekulation:** Ermöglicht das Laden eines Datums und die mögliche Verwendung vor schreibende Speicherzugriffe zu verlegen. Bei diesen unklaren Speicherzugriffen wird eine Speicherposition referenziert, von der nicht bekannt ist, welche dadurch indirekt bezeichnete Speicherstelle durch einen Schreibzugriff verändert wird.

- **Kontrollspekulation:** Wird ein zu ladendes Datum und dessen mögliche Verwendung durch eine Verzweigung gesteuert, so bezeichnet man das vorgezogene Laden des Datums über Verzweigungen hinweg als Kontrollspekulation.

Diese Techniken werden verwendet, um Lade-Latenzzeiten zu verstecken und die Ausführungsgeschwindigkeit zu erhöhen. Dabei die ALAT zum Einsatz. Im Folgenden wird diese Struktur, basierend auf der Implementierung des Intel Itanium beschrieben.

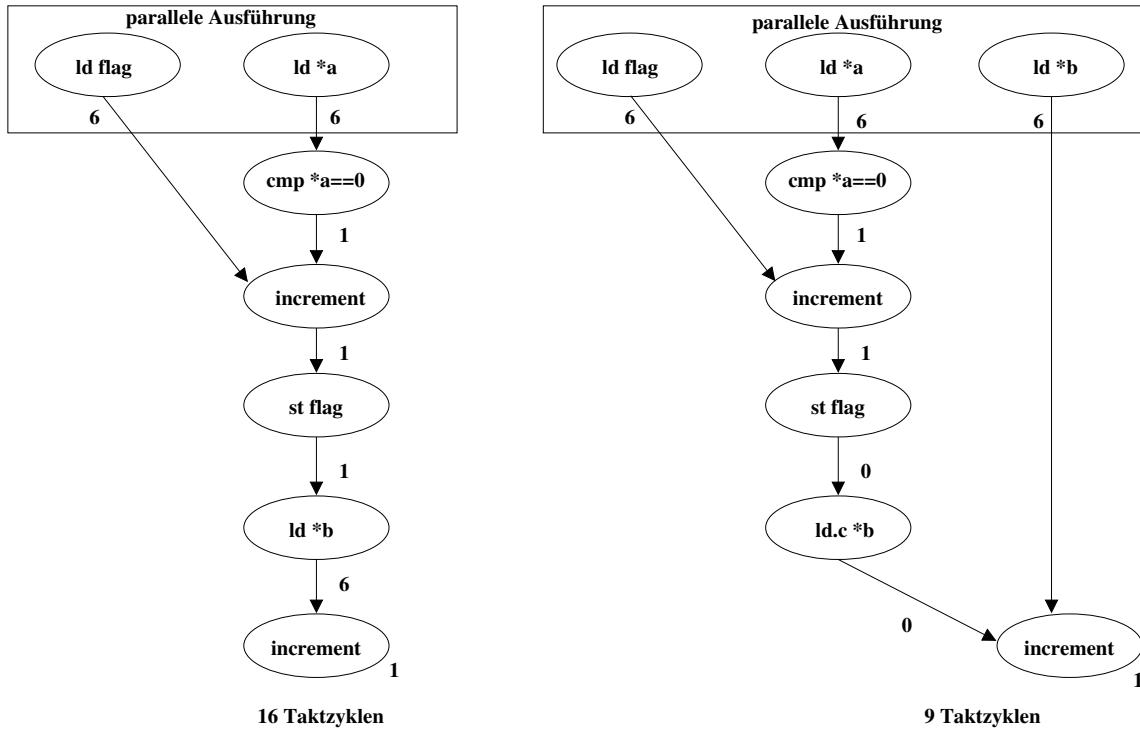

**Die Datenspekulation** Die Datenspekulation setzt eine spezielle Ladeanweisung (*ld.a*) ein, welche *advanced load* genannt wird. Mit dieser Anweisung ist eine überprüfende Instruktion (*chk.a* oder *ld.c*) verbunden, um die spekulativen Werte zu verifizieren. Abbildung 3.4 zeigt ein einfaches Codestück, bei dem das spekulative Laden von Daten zum Einsatz kommen kann. Es ist der Maschinencode für das folgende Beispielprogramm dargestellt:

```

unsigned char flag; //global

int test(int *a, *b)

{

if(*a)

flag++;

return(*b-1);

}

```

Die Referenz *\*b* kann nun vorgezogen und in ein Register zum schnelleren Zugriff gespeichert werden. Es ist zu beachten, daß *\*b* ein Zeiger auf einen Speicherbereich ist und wiederum auf eine Speicherreferenz verweisen kann. Eine Veränderung eines solchen Wertes kann zum Beispiel RAW-Konflikte auslösen. Die Ausführung einer spekulativen Ladeanweisung mit der speziellen Instruktion *ld.a* speichert die Zielregisternummer, einen Teil der Speicheradresse und die Größe des Datums in der ALAT. Dabei findet eine Ersetzung der ursprünglichen Anweisung durch eine Testanweisung – *ld.c* oder *chk.a* statt – für den Fall, daß kein passender Eintrag in der ALAT gefunden werden konnte.

Jeder schreibende Zugriff vergleicht nun die Zieladresse mit jedem Eintrag in der ALAT. Findet sich ein solcher, so wird der entsprechende Eintrag invalidiert – in diesem Falle spricht man von einer Kollision. Bevor ein spekulativ geladenes Datum verwendet werden

Abbildung 3.4: Beispielcode traditionell abgearbeitet und durch Datenspekulation verändert. Die Angegebenen Zahlen stellen die Minimal-Taktzyklen dar, die die Abarbeitung des Maschinenbefehls benötigt. Befehle auf einer Ebene werden parallel abgearbeitet, so daß nur die maximale Anzahl der angegebenen Taktzyklen verbraucht wird.

kann, wird wiederum mittels *ld.c* oder *chk.a* ein gültiger Eintrag in der ALAT gesucht. Ist ein gültiger, durch die Zielregisternummer indizierter Eintrag vorhanden, so trat keine Kollision auf und das Datum ist direkt zu nutzen. Andernfalls schlägt der Test fehl und das korrekte Datum muß erneut aus dem Speicher geladen werden. Die *ld.c* Instruktion lädt das Datum neu aus dem Speicher, die *chk.a* Instruktion springt zu einer speziellen Behandlungsroutine und führt den vom Compiler generierten Code aus [27].

**Die Kontrollspekulation** Der folgende Beispielcode zeigt die Verwendung der Kontrollspekulation:

```

conditional_branch zu_Label //bedingter Sprung zu einem

Label

ld r1=[r5] // Laden des Registers r1 mit dem Inhalt der

Speicheradresse von r5

add r1,r3 //Addition

```

Der Code kann derart verändert werden, daß die *load*-Anweisung vor den bedingten Sprung verschoben wird. Mittels kontrollspekulativen Ladens (*ld.s*) und Überprüfens (*chk.s*) verändert sich der Code zu:

```

ld.s r1=[r5] //vorgezogenes Laden

weitere Instruktionen

conditional_branch zu_Label

chk.s r1, behandlungsroutine

add r1,r3 //Addition

```

Gleichermaßen wie bei der Datenspekulation schreibt die Instruktion `ld.s` und liest die Instruktion `chk.s` Einträge der ALAT. Daher ist ersichtlich, daß die Performance eines Programms von der erfolgreichen Nutzung der ALAT abhängt, weil Registerzugriffe schneller vonstatten gehen als Hauptspeicherzugriffe. Folgende Ereignistypen beschreiben die ALAT: